# Using Graphics Processing Units to solve the classical N-Body Problem in Physics and Astrophysics

Mario Spera<sup>1,2</sup>

<sup>1</sup>INAF-Osservatorio Astronomico di Padova, Vicolo dell'Osservatorio 5, I-35122, Padova, Italy; <sup>2</sup>Sapienza, Universitá di Roma, P.le A. Moro 5, I-00165 Rome, Italy;

mario.spera@oapd.inaf.it mario.spera@live.it

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/34

Graphics Processing Units (GPUs) can speed up the numerical solution of various problems in astrophysics including the dynamical evolution of stellar systems; the performance gain can be more than a factor 100 compared to using a Central Processing Unit only. In this work I describe some strategies to speed up the classical N-body problem using GPUs. I show some features of the N-body code HiGPUs as template code. In this context, I also give some hints on the parallel implementation of a regularization method and I introduce the code HiGPUs-R. Although the main application of this work concerns astrophysics, some of the presented techniques are of general validity and can be applied to other branches of physics such as electrodynamics and QCD.

#### 1 Introduction

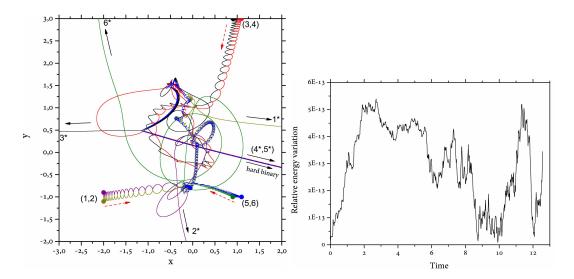

The N-body problem is the study of the motion of N point-like particles interacting through their mutual forces that can be expressed according to a specific physical law. In particular, if the reciprocal interaction is well approximated by the Newton's gravity law, we refer to the classical, gravitational N-body problem. The differential equations that describe the kinematics of the N-body system are

$$\begin{cases} \ddot{\mathbf{r}}_{i} = -G \sum_{\substack{j=1\\j\neq i}}^{N} \frac{m_{j}}{r_{ij}^{3}} \mathbf{r}_{ij} \\ \mathbf{r}_{i}(t_{0}) = \mathbf{r}_{i,0} \qquad i = 1, 2, ..., N \\ \dot{\mathbf{r}}_{i}(t_{0}) = \dot{\mathbf{r}}_{i,0} \end{cases}$$

$$(1)$$

where t is the time,  $\mathbf{r}_i$ ,  $\dot{\mathbf{r}}_i$  and  $\ddot{\mathbf{r}}_i$  are the position, the velocity and the acceleration of the i-th particle, respectively, G is the universal gravitational constant,  $m_j$  indicates the mass of the particle j,  $\mathbf{r}_{i,0}$  and  $\dot{\mathbf{r}}_{i,0}$  represent the initial position and velocity and  $r_{ij}$  is the mutual distance between particle i and particle j. Although we know that the solution of the system of equations (1) exists and is unique, we do not have its explicit expression. Therefore, the best way to solve the N-body problem is numerical. The numerical solution of the system of equations (1) is considered a challenge despite the considerable advances in both software

## **Chapter 1**

## **GPU** in High-Level Triggers

#### **Convenors:**

Ivan Kisel Daniel Hugo Campora Perez Andrea Messina

## The GAP project: GPU applications for High Level Trigger and Medical Imaging

Matteo Bauce<sup>1,2</sup>, Andrea Messina<sup>1,2,3</sup>, Marco Rescigno<sup>3</sup>, Stefano Giagu<sup>1,3</sup>, Gianluca Lamanna<sup>4,6</sup>, Massimiliano Fiorini<sup>5</sup>

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/1

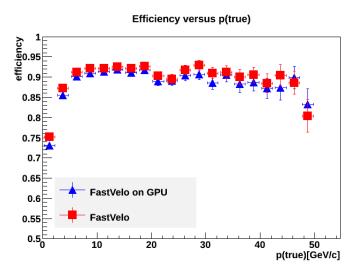

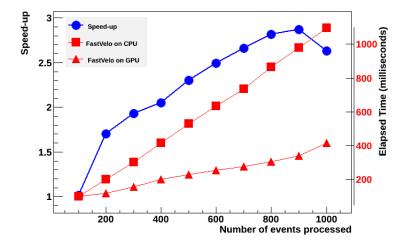

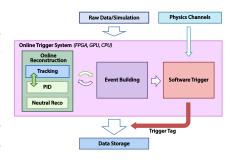

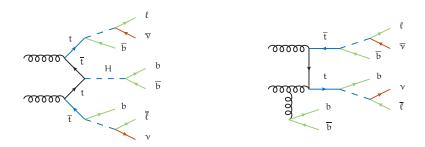

The aim of the GAP project is the deployment of Graphic Processing Units in real-time applications, ranging from the online event selection (trigger) in High-Energy Physics to medical imaging reconstruction. The final goal of the project is to demonstrate that GPUs can have a positive impact in sectors different for rate, bandwidth, and computational intensity. Most crucial aspects currently under study are the analysis of the total latency of the system, the algorithms optimisations, and the integration with the data acquisition systems. In this paper we focus on the application of GPUs in asynchronous trigger systems, employed for the high level trigger of LHC experiments. The benefit obtained from the GPU deployment is particularly relevant for the foreseen LHC luminosity upgrade where highly selective algorithms will be crucial to maintain a sustainable trigger rates with very high pileup. As a study case, we will consider the ATLAS experimental environment and propose a GPU implementation for a typical muon selection in a high-level trigger system.

#### 1 Introduction

The Graphic Processing Units (GPU) are commercial devices optimized for parallel computation, which, given their rapidly increasing performances, are being deployed in many general purpose application. The GAP project is investigating GPU applications in real-time environments, with particular interest in High Energy Physics (HEP) trigger systems, which will be discussed in this paper, but also Medical Imaging reconstruction (CT, PET, NMR) discussed in [1]. The different areas of interest span several orders of magnitude in terms of data processing, bandwidth and computational intensity of the executed algorithms, but can all benefit from the implementation of the massively parallel architecture of GPUs, optimizing different aspects, in terms of execution speed and complexity of the analyzed events. The trigger system of a typical HEP experiment has a crucial role deciding, based on limited and partial information, whether a particular event observed in a detector is interesting enough to be recorded. Every

<sup>&</sup>lt;sup>1</sup>Sapienza Università di Roma, Italy

<sup>&</sup>lt;sup>2</sup>INFN - Sezione di Roma 1, Italy

<sup>&</sup>lt;sup>3</sup>CERN, Geneve, Switzerland

<sup>&</sup>lt;sup>4</sup>INFN - Sezione di Frascati, Italy

<sup>&</sup>lt;sup>5</sup>Università di Ferrara, Italy

<sup>&</sup>lt;sup>6</sup>INFN - Sezione di Pisa, Italy

experiment is characterised by a limited Data Acquisition (DAQ) bandwidth and disk space for storage hence needs real-time selections to reduce data throughput selectively. The rejection of uninteresting events only, is crucial to make an experiment affordable, preserving at the same time its discovery potential. In this paper we report some results obtained from the inclusion of GPU in the ATLAS High Level Trigger (HLT); we will focus on the main challenges to deploy such parallel computing devices in a typical HLT environment and on possible improvements.

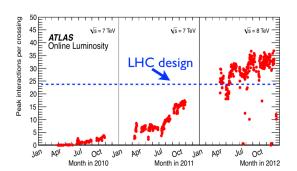

#### 2 ATLAS trigger system

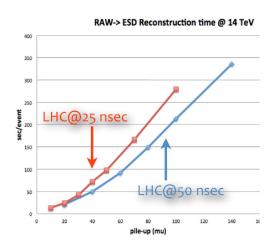

The LHC proton-proton accelerator provides collisions at a rate of 40 MHz, which corresponds, for events of a typical size of 1-2 MByte, to an input data rate of the order of tens of TB/s. The reduction of this input rate to a sustainable rate to be stored on disk, of the order of ~100 kHz, is achieved through a hybrid multi-level event selection system. Lower selection stages (Lower Level Triggers) are usually implemented on customized electronics, while HLT are nowadays implemented as software algorithms executed on farms of commodity PCs. HLT systems, in particular those of LHC experiments, offer a very challenging environment to test cutting-edge technology for realtime event selection. The LHC upgrade with the consequent increase of instantaneous luminosity and collision pile-up, poses new challenges for the HLT systems in terms of rates, bandwidth and signal selectivity. To exploit more complex algorithms aimed at better performances, higher computing capabilities and new strategies are required. Moreover, given the tendency of the computing industry to move away from the current CPU model towards architectures with high numbers of small cores well suited for vectorial computation, it is becoming urgent to investigate the

possibility to implement a higher level of parallelism in the HLT software.

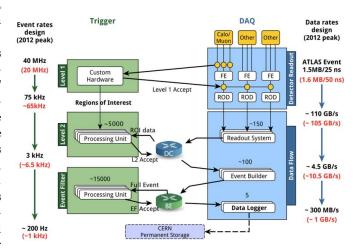

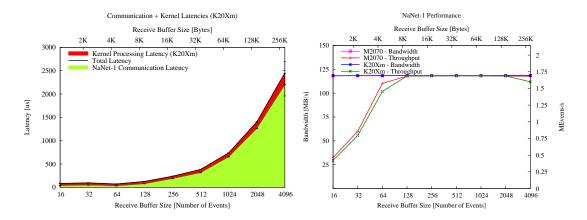

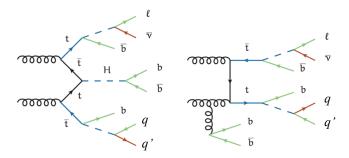

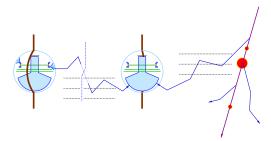

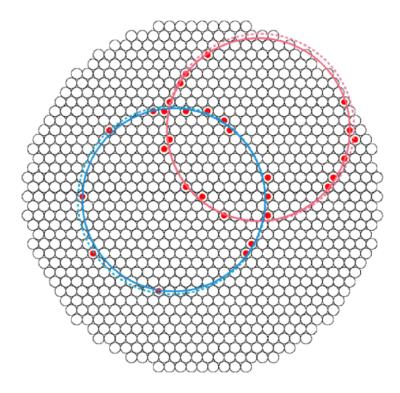

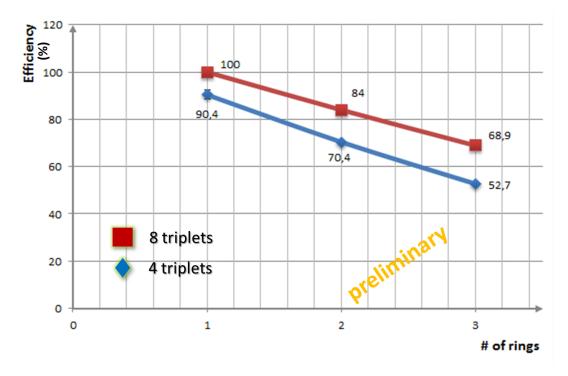

The GAP project is investigating the deployment of GPUs for the HLT in LHC experiments, using as a study case the ATLAS muon HLT. The ATLAS trigger system is organized in 3 levels [2], as shown in Figure 1. The first trigger level is built on custom electronics, while the second level (L2) and the event filter (EF) are implemented in software algorithms executed by a farm of about 1600 PCs with different Xeon processors each with 8 to 12 cores. During the Run II of the LHC (ex-

Figure 1: A scheme of the ATLAS trigger system; values in red are indicating the data-taking conditions during the first run of the LHC ('10-'12) while values in black represents the design conditions, expected to be reached during the upcoming run (starting in 2015).

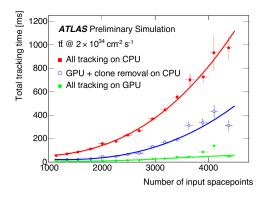

pected to start in 2015) the L2 and EF will be merged in a single software trigger level. Currently, a first upgrade is foreseen in 2018 [3], when real-time tracking capabilities will also be available, followed by a complete renovation of the trigger and detector systems in 2022. We intend to explore the potential improvements attainable in the near future by deploying GPUs in the ATLAS LVL2 muon trigger algorithms. Such algorithms are now implemented as simplified versions and are based on the execution for a large number of times of the same algorithms that reconstruct and match segments of particle trajectories in the detector. The high computing capabilities of GPUs would allow the use of refined algorithms with higher selection efficiency, and thus to maintain the sensitivity to interesting physics signals even at higher luminosity.

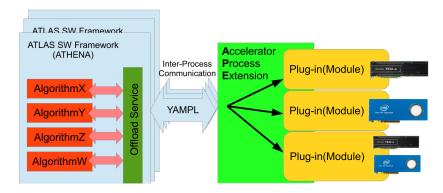

In the current ATLAS data acquisition framework it is not possible to include directly a parallel computing device; the integration of the GPU in this environment is done through a server-client structure (Accelerator Process Experiment - APE [4]) that can manage different tasks and their execution on an external coprocessor, such as the GPU. This implementation is flexible, able to deal with different devices having optimized architecture, with a reduced overhead. With the help of this structure it is possible to isolate any trigger algorithm and optimize it for the execution on a GPU (or other parallel architecture device).

This will imply the translation into a parallel computing programming language (CUDA<sup>1</sup> [7]) of the original algorithm and the optimization of the different tasks that can be naturally parallelized. In such a way the dependency of the execution time on the complexity of the processed events will be reduced. A similar approach has been investigated in the past for the deployment of GPUs in different ATLAS algorithms with promising results [5]. The evolution of the foreseen ATLAS trigger system, that will merge the higher level trigger layers in a unique software processing stage, can take even more advantage from the use of a GPU since a more complex algorithm, with offline-like resolution can be implemented on a thousand-core device with significant speedup factors. The timing comparison between the serial and the parallel implementation of the trigger algorithm is done on the data collected in the past year.

#### 3 Muon reconstruction isolation algorithm

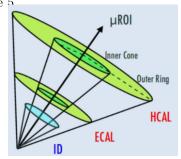

The benchmark measurements that has been carried out has focused on one of the algorithms developed for muon reconstruction in ATLAS. In the L2 trigger a candidate muon particle is reconstructed combining three different and sequential algorithms: the first one reconstructs a charged particle track segment in the muon spectrometer [6], a second algorithm matches in space such track segment to a charged particle track reconstructed in the ATLAS Inner Detector (ID) [6], the third evaluates the energy deposits in the electromagnetic and hadronic calorimeters (ECAL, HCAL) [6], as well as the track density in the detector region around the candidate muon trajectory, to check the consistency with a muon crossing the whole ATLAS detector. This third step of the muon reconstruction has been considered for our first test deploying a GPU in the ATLAS trigger system.

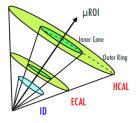

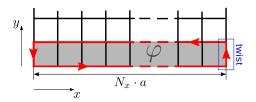

Figure 2: Scheme of the cone used in the muon isolation algorithm.

<sup>&</sup>lt;sup>1</sup>We perform the tests described in this article on a server set up for this purpose including an NVIDIA graphic accelerator, hence the GPU code has been developed in CUDA.

The muon isolation algorithm starts from the spatial coordinates of the candidate muon trajectory and consider a cone of fixed width  $\Delta R = \sqrt{\Delta \phi^2 + \Delta \eta^2}$  in the  $(\eta,\phi)$  ([6]) space around such trajectory. In order to pass the muon track isolation requirement there should be only a limited number of tracks in the considered cone, and these must be consistent with background in the inner ATLAS tracking system. The calorimeter isolation is applied summing the energy deposits in the electromagnetic and hadronic calorimeter cells lying within the considered cone, and requiring this is only a small fraction of the estimated candidate muon energy<sup>2</sup>. Figure 2 shows the definition of the cone used to evaluate the muon isolation in the calorimeter and in the inner detector.

The integration of the GPU and the execution of such algorithm within the ATLAS trigger framework can be summarized in the following steps:

- 1. retrieve information from the detector: access to the calorimeter cells information;

- 2. format information needed by the algorithm, namely the cell content, data-taking conditions, and calorimeter configuration information, into a memory buffer;

- 3. transfer the prepared buffer to the server (APE) which handles the algorithm execution and transfer the buffer to the GPU;

- 4. algorithm execution on the GPU (or on a CPU in the serial version of the algorithm);

- 5. transfer of the algorithm results through the APE server back into the ATLAS trigger framework;

Step 1 is the same also in the current implementation of the muon isolation algorithm; in the standard ATLAS trigger implementation (serial) this step is followed directly by the algorithm execution (step 4) on the CPU. Step 2 is needed to optimize the data-transfer toward the GPU; it is important at this stage to convert the object-oriented structures to a plain buffer containing the minimum amount of information needed by the algorithm to minimize the CPU-GPU communication la-Step 3 is implemented through litency. braries dedicated to the client-server communication, as a part of the APE server. Such server manages the assignement of the task to the GPU for the execution and waits to retrieve the results. To accomplish step 4, the simple algorithm which evaluates the calorimeter isolation has been translated into the CUDA language optimizing the management of the GPU resources in terms of computing CUDA cores and memory usage. Step

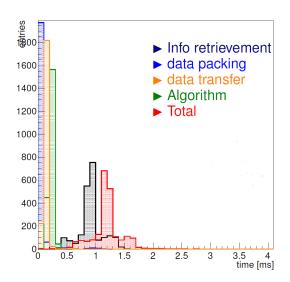

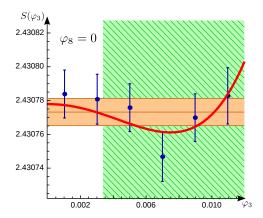

Figure 3: Measurement of the muon isolation algorithm execution time using a Nvidia GTX Titan GPU.

<sup>&</sup>lt;sup>2</sup>The requirement on this energy fraction varies depending on the region of the detector and the desired quality of the reconstructed muon, but this aspect is not relevant for the purpose of these tests.

5 is implemented within the APE server, similarly to step 3, and completes the CPU-GPU communication, reporting the algorithm results in the original framework.

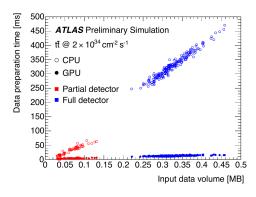

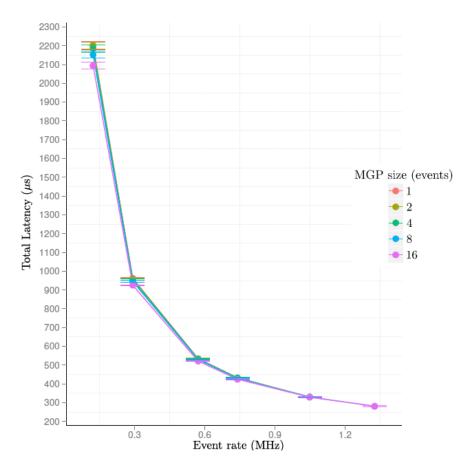

The measurement of the trigger algorithm execution latency has been performed using a server machine containing an Intel Xeon E5-2620 CPU and a Nvidia GTX Titan GPU, reprocessing a sample of ATLAS recorded data with no dedicated optimization of the machine. Figure 3 shows the execution latency measured for the several steps and their sum. The overall execution time resulted in being  $\Delta t_{GPU}^{tot} \approx 1.2 \pm 0.2$  ms when using the GPU, with respect to  $\Delta t_{CPU}^{tot} \approx 0.95 \pm 0.15$  ms, obtained with the standard execution on CPU. As it is shown in Figure 3 the largest fraction of the time ( $\sim 900 \ \mu s$ ) is spent to extract the detector data and convert them from the object-oriented structure to a flat format which is suitable for the transfer to the GPU. This contribution to the latency is independent from the the serial or parallel implementation of the algorithm, since it's related to data structure decoding; the current version of the ATLAS framework heavily relies on object-oriented structures, which are not the ideal input for GPUs. The contribution due to the CPU-GPU communication through the client-server structure is found to be  $\Delta t_{GPU}^{trans.} \sim 250 \ \mu s$ , which is within the typical time budget of the ATLAS HLT ( $\mathcal{O}(10 \text{ ms})$ ). This result confirms the possibility to include GPUs into a HLT system for the execution of parallel algorithms, hence motivates further studies in this direction.

#### 4 Conclusions and Perspectives

From this first study we succesfully deployed a GPU within the ATLAS pre-existing trigger and DAQ framework through a flexible client-server scheme. We observed that the CPU-GPU communication does not introduce a dramatic overhead, which is indeed well within the typical execution latencies of software trigger algorithms,  $\mathcal{O}(10 \text{ ms})$ . This result shows that is feasible to consider the GPUs as extremely powerful computing devices for the evolution of the current asynchronous trigger systems. Most of the execution time is devoted to the data extraction from object-oriented structures, which is currently an external constraint from the ATLAS trigger framework. This observation, confirmed by similar studies in the ATLAS experiment, focused the attention on this topic; a common effort is ongoing to overcome this problem and benefit at most from the GPU computing power. At the moment two viable approaches are being considered: on one hand it's interesting to consider more complex algorithms that can reduce the time spent for data structure handling to a negligible fraction; on the other hand it is possible to handle *simpler* data structures (raw byte

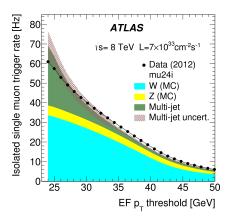

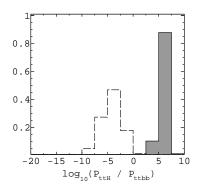

Figure 4: Isolated single muon trigger observed rate as a function of the muon transverse momentum  $(p_T)$ , compared to simulations for the different expected contributions.

streams from the detector), bypassing most of the currently existing framework. As an example of the first approach the possibility to execute at the trigger level, a refined evaluation of

the muon isolation, which would be not sustainable in single-threaded execution on a CPU, is currently under investigation. The muon isolation evaluated in the offline data reprocessing takes into account also environmental corrections due to multiple interactions leading to additional noise in the calorimeter and tracking system. Figure 4 shows the trigger rate as a function of the muon transverse momentum,  $p_T$ , for the isolated muon trigger in a data-taking period during 2012. One can see that a relevant fraction of the trigger rate is due to spurious events (multi-jet production). A refined calculation of the muon isolation would reduce such trigger rate, maintaining the efficiency for prompt muon reconstruction high .

As a typical scenario for the second approach, it is possible to decode and process simple data from the muon spectrometer (position and time information) [6] to reconstruct the muon track segment. A similar strategy has been developed in a standalone test considering track reconstruction in the ATLAS Inner Detector, with interesting results [5].

#### 5 Acknowledgements

The GAP project and all the authors of this article are partially supported by MIUR under grant RBFR12JF2Z Futuro in ricerca 2012.

#### References

- [1] Proceeding of Estimated speed-up from GPU computation for application to realtime medical imaging from this same workshop (2014).

- [2] ATLAS Collaboration, JINST 3 P08003 (2008).

- [3] ATLAS Collaboration, -CERN-LHCC-2011-012 (2012).

- [4] The client-server structure is obtained using APE, an ATLAS tool developed independently from this project.

- [5] D. Emeliyanov, J. Howard, J. Phys.: Conf. Ser. 396 012018 (2012).

- $[6]\;$  ATLAS Collaboration, JINST 3 S08003 (2008).

- [7] http://docs.nvidia.com/cuda/cuda-c-programming-guide

## GPU-based quasi-real-time Track Recognition in Imaging Devices: from raw Data to Particle Tracks

Cristiano Bozza<sup>1</sup>, Umut Kose<sup>2</sup>, Chiara De Sio<sup>1</sup>, Simona Maria Stellacci<sup>1</sup>

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/2

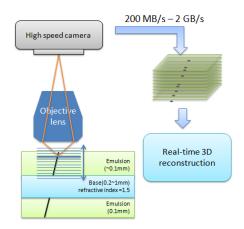

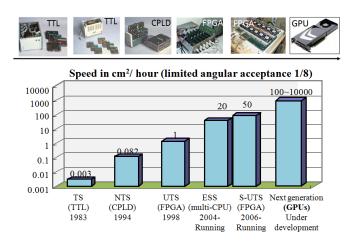

Nuclear emulsions as tracking devices have been used by recent experiments thanks to fast automatic microscopes for emulsion readout. Automatic systems are evolving towards GPU-based solutions. Real-time imaging is needed to drive the motion of the microscope axes and 3D track recognition occurs quasi-online in local GPU clusters. The algorithms implemented in the Quick Scanning System are sketched. Most of them are very general and might turn out useful for other detectors.

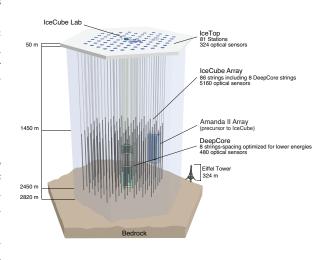

#### 1 Nuclear emulsions as tracking detectors

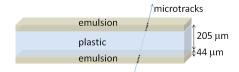

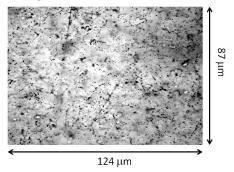

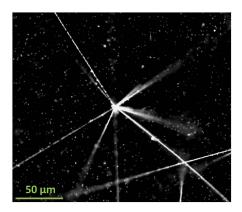

Nuclear emulsions have a long history in highenergy physics and recently experienced revived interest in the CHORUS[1], DONUT, PEANUT[2] and OPERA[3] experiments. They provide the best spatial resolution currently available, of the order of 0.1  $\mu$ m. On the other hand, they have no time resolution, recording all charged tracks since the time of production until photographic development. In common setups, a detector is made up of one or more stacks of films, placed approximately orthogonally to the direction of the incoming particles. Each film has two layers of emulsion coating a transparent plastic base (Fig. 1). Typical dimensions are 50  $\mu$ m for the thickness of emulsion layers and 200  $\mu m$  for the base. A nuclear emulsion contains AgBr crystals in a gel matrix. Charged particles sensitise the crystals by ionisation, producing a latent image. Development of the film produces metallic Ag grains in place of the latent image, resulting in aligned sequences of grains (microtracks), typically  $0.3\sim1~\mu m$  in diameter (Fig. 2). In an optical transmission micro-

Figure 1: Nuclear emulsion film.

Figure 2: Nuclear emulsion image. Highenergy tracks are orthogonal to plane.

scope, grains appear as dark spots on light background. In white light, the average alignment residuals of grains with respect to the straight line fit is of the order of 50 nm. The depth of

<sup>&</sup>lt;sup>1</sup>Department of Physics University of Salerno, Via Giovanni Paolo II 132, 84084 Fisciano, Italy

<sup>2</sup>CERN, 1211 Geneve 23, Switzerland

field of the optics is usually below 5  $\mu$ m. The full thickness of the emulsion layer is spanned by moving the optical axis, thus producing optical tomographies with a set of equally spaced planes (15~31 usually). The image of a particle track in a focal plane is a single grain, not necessarily present in each plane (ionisation is a stochastic process). Because the chemical process of development is just faster for sensitised grains, but it occurs in general for every crystal in a random fashion, many grains appear without having been touched by any particle. Such so-called fog grains are overwhelming in number: as a reference, the ratio of fog grains to microtrack grains ranges from  $10^3$  through  $10^5$ . Only 3D alignment is able to single out the few microtrack grains, but also many fake microtracks due to random alignments survive in a single film. Stacking several films allows using coincidence methods to improve background rejection.

It is worth noticing that this resembles the situation of an electronic detector in which background hits due to noise or pile-up overwhelm track hits. Normally, electronic detectors use a time trigger to reduce combinatorial complexity, but in emulsion this is not possible. It is reasonable to think that a tracking algorithm working in emulsion finds an even easier environment if fed with data from other detectors, such as cloud chambers or planes of silicon pads.

#### 2 Data from nuclear emulsion

A nuclear emulsion film has typically a rectangular shape, spanning several tens of cm in both directions. The whole surface is scanned by acquiring optical tomographies in several fields of view with a repetitive motion. An electronic shutter ensures that images are only negligibly affected by motion blur. In the ESS (European Scanning System [4], [5], [6], [7], [8]), developed in the first decade of the  $21^{\rm st}$  century, the XY microscope axes hold steady while the Z axis (optical axis) moves and images are grabbed on the fly and sent to vision processors. Its evolution, named QSS (Quick Scanning System), moves the X axis continuously. Hence, each view (an optical tomography) of ESS is a cuboid, whereas those of QSS are skewed prisms. Images are acquired by fast monochromatic sensors (CMOS) mounted on the optical axis, capable of  $200{\sim}400$  frames per second, each frame being  $1{\sim}4$  MPixel (or more for future sensors) using 8 bits/pixel. The resulting data rate ranges from 0.5 GB/s to 2 GB/s. The linear size of the image stored in a pixel, with common optics, is of the order of 0.3  $\mu$ m. The full size of the field of view is  $400{\times}320~\mu$ m<sup>2</sup> for ESS,  $770{\times}550~\mu$ m<sup>2</sup> for QSS.

2D image processing used to be shared in the case of ESS by an industrial vision processor (Matrox Odyssey) based on an FPGA and by the host workstation CPU. It consists of several substeps:

- 1. grey level histogram computation and stretching used to compensate for varying light yield of the lamp;

- 2. FIR (*Finite Impulse Response*) processing with a 5×5 kernel and comparison of filter output to a threshold selects dark pixels on light background, producing a binary image;

- 3. reduction of sequences of pixels on horizontal scan lines to segments;

- 4. reduction of segments in contact on consecutive scan lines to clusters of dark pixels produces grains to be used for tracking.

In the ESS, steps 1 and 2 are performed on the FPGA-based device. Steps 3 and 4 are executed by the host workstation CPU. For the same task, QSS uses a GPU board hosted in

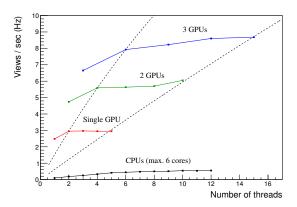

the workstation that controls the microscope: common choices are double-GPU boards such as NVidia GeForce GTX 590 or GTX 690. A single board can do everything without intervention of the host workstation CPU. The first 3 steps are quite natural applications for GPU's. One single GPU can be up to 7 times faster than the Odyssey, reducing the price by an order of magnitude. Steps 4 and 5 require special attention in code development, because they are reduction operations with an a priori unknown number of output objects. In step 4 each thread takes care of a single scan line of the image. In step 5 a recursive implementation has been chosen: at iteration n, the segments on scan line  $i \times 2^n$  are compared to those on line  $i \times 2^n - 1$ and the related dark clusters are merged together. Indeed, steps 4 and 5 are the slowest, and they define the total processing speed, which is 400 MB/s for GTX 590. The system is scalable, and more GPU boards or more powerful ones can be added if needed. The output of this step is, for each view, a set of clusters of dark pixels on light background, each one being encoded with its X, Y, Z coordinates and size in pixels. Automatic readout uses the distribution of clusters to continuously adjust the Z axis drive of the tomography. 60~124 MB of image data are encoded to 8~16 MB cluster block, ready for local storage or to be transmitted over the network for further processing. In the latter case, a RAM disk area is used as a buffer to distribute data to a cluster of GPU's. Tracking servers and the workload manager provide a command-line interface for administration and have an embedded lightweight Web server, originally developed for the SySal project ([7]), that provides a graphical interface for human access and is the backbone for an HTTP-based network protocol for control messages needed for workload assignment.

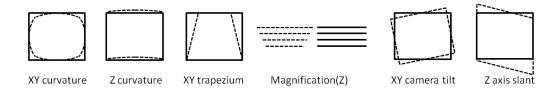

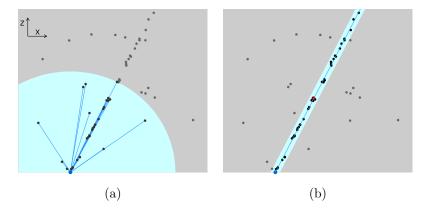

Particle tracks can cross the boundary of a view, and tracking must be able to do the same. The alignment tolerance to recognise real tracks and discard background cannot exceed 0.5  $\mu$ m and is usually smaller. The motion control electronics is capable of position feedback, but triaxial vibrations due to combined motion arise, well beyond 1  $\mu$ m in a single image. Corrections to raw data are needed before they can be used to recognise microtracks. Some such corrections, sketched in Fig. 3, depend on optical aberrations and are systematic effects that can be computed off-line from small data-sets and then applied on each incoming cluster block (view):

- 1. Spherical aberrations: XY and Z curvature;

- 2. trapezium distortions: dependence of magnification factor on X and Y;

- 3. magnification-vs.-Z dependence;

- 4. camera tilt: rotation in the XY plane;

- 5. optical axis slant: X-Z and Y-Z couplings due to inclined optical axis.

Figure 3: Optical distortion of emulsion image.

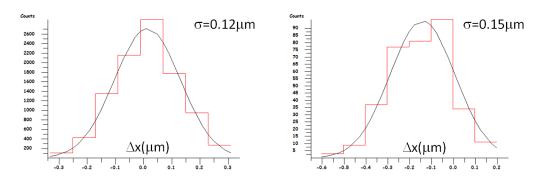

Most of the computing power needed for data correction is taken by other effects that are purely stochastic: vibrations due to motion, increased by mechanical wear and aging are unpredictable and spoil the alignment of images within the same view and between consecutive views. Because the depth-of-field usually exceeds the Z pitch between two images in the same sequence taken while the Z axis moves, a sizable fraction of the dark clusters in one image will appear also in the next. Pattern matching works out the relative shift between the images, usually within 1  $\mu$ m. This procedure requires scanning a square region of possible values of the plane shift vector. Combinatorial complexity is reduced by arranging clusters in a 2D grid of cells and considering only pair matching within each cell. The shift vector that maximizes the number of combinations is the best approximation of the misalignment between the images. Likewise, despite position feedback of all axes, a whole tomography is misaligned with respect to the next. Film scanning is performed so as to leave  $30{\sim}40~\mu$ m overlap between adjacent views. The dark clusters found in the overlap region are used to perform 3D pattern matching, in the same way as for 2D pattern matching. The standard deviation of the distribution of residuals is of the order of 150 nm (Fig. 4) for X and Y, and 2.6  $\mu$ m for Z.

Figure 4: Left: precision of image-to-image alignment in the same tomographic sequence. Right: precision of relative alignment of two tomographic sequences.

#### 3 Track reconstruction

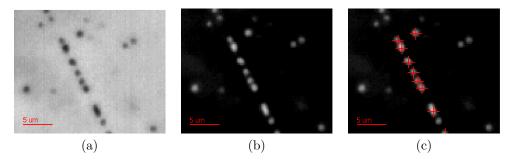

Reconstructing 3D tracks from a set of primitive objects such as emulsion grain images or electronic detector hits is a common task in high-energy physics. The method depicted in the following would work in all cases of straight tracks, i.e. absent or weak magnetic field and scattering effects negligible with respect to the granularity of the detector. Because ionisation is a stochastic process, the algorithm does not require that a microtrack has a dark cluster in every image; furthermore, the notion of sampling planes is deliberately discarded to keep the algorithm general. It just needs to work on 3D pointlike objects, each having a weight, which corresponds to the number of pixels of the dark cluster in this case (e.g. it may be the deposited energy in a silicon counter). Each pair of dark clusters defines a seed, i.e. a straight line in 3D space; other clusters are expected to be aligned with it within proper tolerance (Fig. 5-left). In thin emulsion layers, microtracks are formed with  $6\sim40$  clusters, depending on the local sensitivity, on statistical fluctuations and on track angle (the wider the inclination with respect to the

thickness dimension, the longer the path length). Furthermore, high-energy particles ionise less than slow ones. Such reasons suggest not to filter out too many possible pairs of clusters as track seeds, considering all those that are within geometrical acceptance. Physics or experimental conditions constrain the angular acceptance to a region of interest. Optimum thread allocation to computing cores demands that constraints be enforced constructively instead of generating all seeds and discarding invalid ones. Dark clusters are arranged in a 2D grid of prisms, each one spanning the whole emulsion thickness (Fig. 5-right). The angular region of interest is scanned in angular steps. At each step the prisms are generated skewed with the central slope of the step. This ensures that seeds that are very far from the acceptance window will not even be built and followed.

Figure 5: Left: microtrack seeds and grains. Right: 2D grid of prisms to build seeds. A prism containing a track is shown darker.

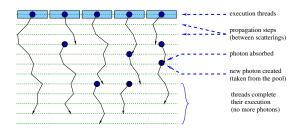

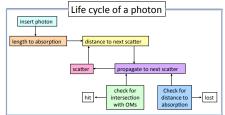

With common operational parameters, the number of useful combinations ranges within  $10^7$  and  $10^9$  per tomographic sequence, depending on the amount of random alignments and fog. For each seed, one thread scans the containing prism to find aligned clusters and build the microtrack. This procedure naturally produces clones of the same track, normally in the range  $2\sim4:1$ . They are discarded by comparing the geometrical parameters of all neighbor microtracks, neighborhood being defined by means of a 2D spatial grid.

#### 4 Performances and outlook

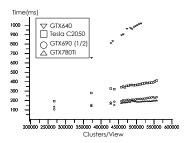

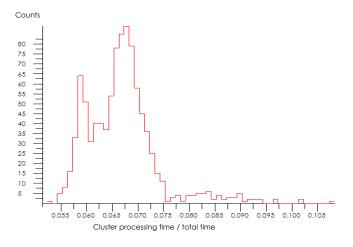

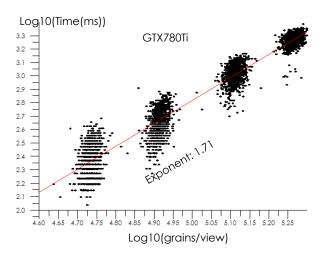

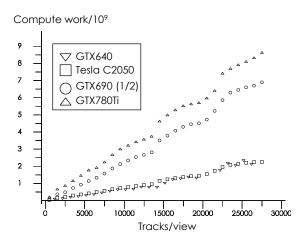

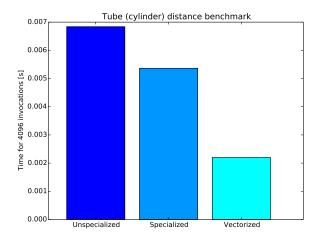

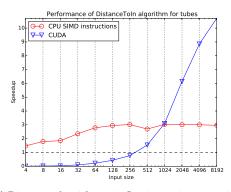

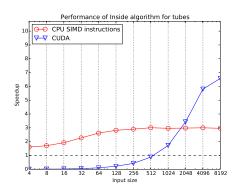

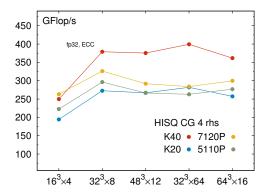

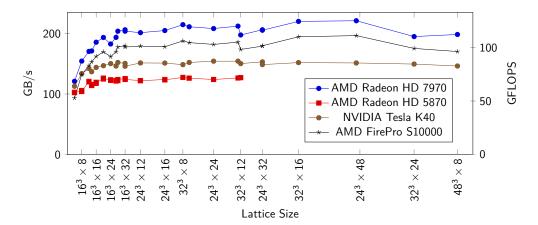

Performances in terms of processing time vs. grain or microtrack density has been estimated using several NVidia GPU's. The results are shown in Figures 6, 7, 8 and 9.

Denoting the grain density (grains per tomography) with N, the number of seed combinations is of order  $N^2$ , and the search for clusters to attach to the seed is of order  $N^3$ . Results show that processing steps of high computational complexity are not overwhelming for typical operational conditions.

While one would expect the processing time to scale inversely with the number of available cores, more recent GPU's perform proportionally worse than older ones. The reason for that is to be sought mostly in branch divergence, which affects more the multiprocessors with larger number of cores. In some cases the divergence is due to threads exiting while others keep running. This could be eliminated, but it's not clear whether the additional complications of code would pay off. In other cases the divergence is due to the specific coding style used in

Figure 6: Absolute time (ms) for cluster correction and alignment. For GTX690, only one GPU is considered.

Figure 7: Fraction of total time used for cluster correction and alignment.

the implementation, and could be reduced by fine-tuning the logic: e.g, the kernel that merges track clones takes about 1/3 of the total time, and removing or taming its divergence offers good chances of overall speed-up. The relative improvements of a GPU-based system over traditional technologies can effectively be estimated by the cost of hardware. For QSS, taking data at  $40\sim90~{\rm cm^2/h}$  with 1 GTX 590 for cluster recognition + 6 GTX 690 for alignment and tracking costs about 5.5 times less than the hardware of ESS taking data at  $20~{\rm cm^2/h}$  on the same emulsion films. The power consumption is similar, although it is worth noticing the data taking speed increase. The GPU-based system is also more modular and scalable.

#### GPU-BASED QUASI-REAL-TIME TRACK RECOGNITION IN IMAGING DEVICES: FROM . . .

Figure 8: Dependency of tracking time (GTX780Ti) on the number of grain clusters/view (dark clusters with minimum size constraint).

Figure 9: Compute work ( $Cores \times Clock \times Time$ , arbitrary units) for several boards. For GTX690, only one GPU is considered.

#### CRISTIANO BOZZA, UMUT KOSE, CHIARA DE SIO, SIMONA MARIA STELLACCI

#### References

- [1] E. Eskut  $et\ al.,\ Nucl.\ Phys.\ B$  **793** 326 (2008).

- [2] A. Aoki et al., New. J. Phys.  ${\bf 12}$  113028 (2010).

- $[3]\,$  R. Acquafredda et~al., J. Inst. 4 P04018 (2009).

- [4] N. Armenise et al., Nucl. Inst. Meth. A **552** 261 (2005).

- [5] L. Arrabito et al., Nucl. Inst. Meth. A 568 578 (2007).

- [6] L. Arrabito  $et~al.,~{\rm J.~Inst.}~{\bf 2}~{\rm P05004}~(2005).$

- [7] C. Bozza  $et\ al.,$  Nucl. Inst. Meth. A.  ${\bf 703}\ 204\ (2013).$

- $[8]\,$  M. De Serio et~al., Nucl. Inst. Meth. A  $\bf 554$  247 (2005).

#### GPGPU for track finding in High Energy Physics

L. Rinaldi<sup>1</sup>, M. Belgiovine<sup>1</sup>, R. Di Sipio<sup>1</sup>, A. Gabrielli<sup>1</sup>, M. Negrini<sup>2</sup>, F. Semeria<sup>2</sup>, A. Sidoti<sup>2</sup>, S. A. Tupputi<sup>3</sup>, M. Villa<sup>1</sup>

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/3

The LHC experiments are designed to detect large amount of physics events produced with a very high rate. Considering the future upgrades, the data acquisition rate will become even higher and new computing paradigms must be adopted for fast data-processing: General Purpose Graphics Processing Units (GPGPU) is a novel approach based on massive parallel computing. The intense computation power provided by Graphics Processing Units (GPU) is expected to reduce the computation time and to speed-up the low-latency applications used for fast decision taking. In particular, this approach could be hence used for high-level triggering in very complex environments, like the typical inner tracking systems of the multi-purpose experiments at LHC, where a large number of charged particle tracks will be produced with the luminosity upgrade. In this article we discuss a track pattern recognition algorithm based on the Hough Transform, where a parallel approach is expected to reduce dramatically the execution time.

#### 1 Introduction

Modern High Energy Physics (HEP) experiments are designed to detect large amount of data with very high rate. In addition to that weak signatures of new physics must be searched in complex background condition. In order to reach these achievements, new computing paradigms must be adopted. A novel approach is based on the use of high parallel computing devices, like Graphics Processing Units (GPU), which delivers such high performance solutions to be used in HEP. In particular, a massive parallel computation based on General Purpose Graphics Processing Units (GPGPU) [1] could dramatically speed up the algorithms for charged particle tracking and fitting, allowing their use for fast decision taking and triggering. In this paper we describe a tracking recognition algorithm based on the Hough Transform [2, 3, 4] and its implementation on Graphics Processing Units (GPU).

#### 2 Tracking with the Hough Transform

The Hough Transform (HT) is a pattern recognition technique for features extraction in image processing, and in our case we will use a HT based algorithm to extract the tracks parameters from the hits left by charged particles in the detector. A preliminary result on this study has been already presented in [5]. Our model is based on a cylindrical multi-layer silicon detector

<sup>&</sup>lt;sup>1</sup>Bologna University and INFN, via Irnerio 46, 40127 Bologna, Italy

<sup>&</sup>lt;sup>2</sup>INFN-Bologna, v.le Berti Pichat 6/2, 40127 Bologna, Italy

<sup>&</sup>lt;sup>3</sup>INFN-CNAF, v.le Berti Pichat 6/2, 40127 Bologna, Italy

installed around the interaction point of a particle collider, with the detector axis on the beamline. The algorithm works in two serial steps. In the first part, for each hit having coordinates  $(x_H, y_H, z_H)$  the algorithm computes all the circles in the x-y transverse plane passing through that hit and the interaction point, where the circle equation is  $x^2 + y^2 - 2Ax - 2By = 0$ , and A and B are the two parameters corresponding to the coordinates of the circle centre. The circle detection is performed taking into account also the longitudinal  $(\theta)$  and polar  $(\phi)$  angles. For all the  $\theta$ ,  $\phi$ , A, B, satisfying the circle equation associated to a given hit, the corresponding  $M_H(A, B, \theta, \phi)$  Hough Matrix (or Vote Matrix) elements are incremented by one. After computing all the hits, all the  $M_H$  elements above a given threshold would correspond to real tracks. Thus, the second step is a local maxima search among the  $M_H$  elements.

In our test, we used a dataset of 100 simulated events (pp collisions at LHC energy, Minimum Bias sample with tracks having transverse momentum  $p_T > 500$  MeV), each event containing up to 5000 particle hits on a cylindrical 12-layer silicon detector centred on the nominal collision point. The four hyper-dimensions of the Hough space have been binned in  $4 \times 16 \times 1024 \times 1024$  along the corresponding  $A, B, \theta, \phi$  parameters.

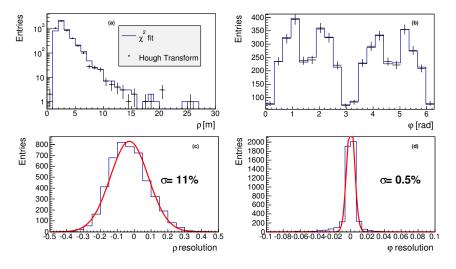

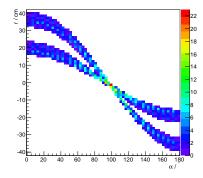

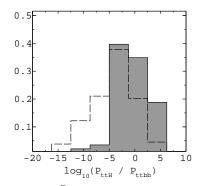

The algorithm performance compared to a  $\chi^2$  fit method is shown in Fig. 1: the  $\rho = \sqrt{A^2 + B^2}$  and  $\varphi = \tan^{-1}(B/A)$  are shown together with the corresponding resolutions.

Figure 1: Hough Transform algorithm compared to  $\chi^2$  fit. (a)  $\rho$  distribution; (b)  $\varphi$  distribution; (c)  $\rho$  resolution; (d)  $\varphi$  resolution.

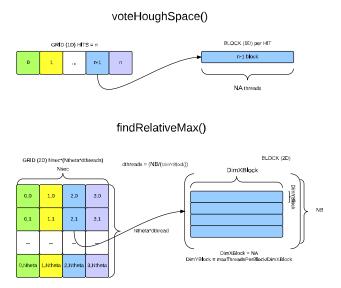

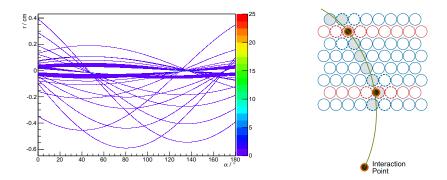

#### 3 SINGLE-GPU implementation

The HT tracking algorithm has been implemented in GPGPU splitting the code in two kernels, for Hough Matrix filling and searching local maxima on it. Implementation has been performed both in CUDA [1] and OpenCL [6]. GPGPU implementation schema is shown in Fig. 2.

Concerning the CUDA implementation, for the  $M_H$  filling kernel, we set a 1-D grid over all the hits, the grid size being equal to the number of hits of the event. Fixed the  $(\theta, \phi)$  values, a thread-block has been assigned to the A values, and for each A, the corresponding

B is evaluated. The  $M_H(A,B,\theta,\phi)$  matrix element is then incremented by a unity with an atomicAdd operation. The  $M_H$  initialisation is done once at first iteration with cudaMallocHost (pinned memory) and initialised on device with cudaMemset. In the second kernel, the local maxima search is carried out using a 2-D grid over the  $\theta,\phi$  parameters, the grid dimension being the product of all the parameters number over the maximum number of threads per block  $(N_\phi \times N_\theta \times N_A \times N_B)$ /maxThreadSPerBlock, and 2-D threadblocks, with dimXBlock= $N_A$  and dimYBlock=MaxThreadPerBlock/ $N_A$ . Each thread compares one  $M_H(A,B,\theta,\phi)$  element to its neighbours and, if the biggest, it is stored in the GPU shared memory and eventually transferred back. With such big arrays the actual challenge lies in optimizing array allocation and access and indeed for this kernel a significant speed up has been achieved by tuning matrix access in a coalesced fashion, thus allowing to gain a crucial computational speed-up. The OpenCL

Figure 2: GPGPU implementation schema of the two Hough Transform algorithm kernels.

implementation has been done using a similar structure used for CUDA. Since in OpenCL there is no direct pinning memory, a device buffer is mapped to an already existing *memallocated* host buffer (clEnqueueMapBuffer) and dedicated kernels are used for matrices initialisation in the device memory. The memory host-to-device buffer allocation is performed concurrently and asynchronously, saving overall transferring time.

#### 3.1 SINGLE-GPU results

The test has been performed using the NVIDIA [1] GPU boards listed in table 1. The GTX770 board is mounted locally on a desktop PC, the Tesla K20 and K40 are installed in the INFN-CNAF HPC cluster.

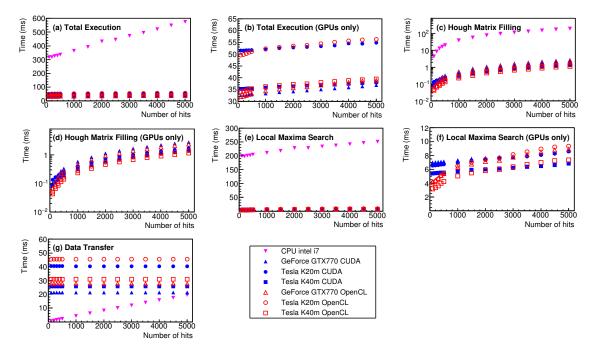

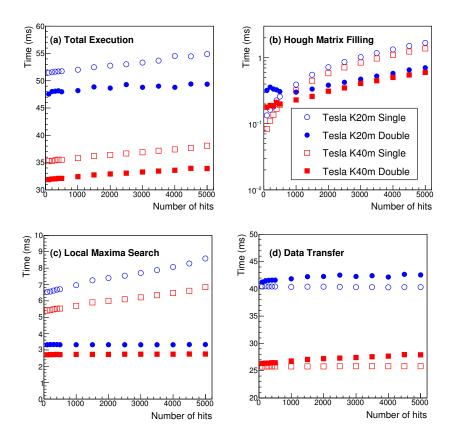

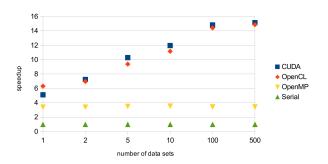

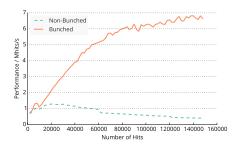

The measurement of the execution time of all the algorithm components has been carried out as a function of the number of hits to be processed, and averaging the results over 100 independent runs. The result of the test is summarised in Fig. 3. The total execution time comparison between GPUs and CPU is shown in Fig. 3a, while in Fig. 3b the details about

| Device                | NVIDIA         | NVIDIA     | NVIDIA     |

|-----------------------|----------------|------------|------------|

| specification         | GeForce GTX770 | Tesla K20m | Tesla K40m |

| Performance (Gflops)  | 3213           | 3542       | 4291       |

| Mem. Bandwidth (GB/s) | 224.2          | 208        | 288        |

| Bus Connection        | PCIe3          | PCIe3      | PCIe3      |

| Mem. Size (MB)        | 2048           | 5120       | 12228      |

| Number of Cores       | 1536           | 2496       | 2880       |

| Clock Speed (MHz)     | 1046           | 706        | 1502       |

Table 1: Computing resources setup.

the execution on different GPUs are shown. The GPU execution is up to 15 times faster with respect to the CPU implementation, and the best result is obtained for the CUDA algorithm version on the GTX770 device. The GPUs timing are less dependent on the number of the hits with respect to CPU timing.

The kernels execution on GPUs is even faster with respect to CPU timing, with two orders of magnitude GPU-CPU speed up, as shown in Figs. 3c and 3e. When comparing the kernel execution on different GPUs (Figs. 3d) and 3f), CUDA is observed to perform slightly better than OpenCL. Figure 3g shows the GPU-to-CPU data transfer timings for all devices together with the CPU I/O timing, giving a clear idea of the dominant part of the execution time.

#### 4 MULTI-GPU implementation

Assuming that the detector model we considered could have multiple readout boards working independently, it is interesting to split the workload on multiple GPUs. We have done this by splitting the transverse plane in four sectors to be processed separately, since the data across sectors are assumed to be read-out independently. Hence, a single HT is executed for each sector, assigned to a single GPU, and eventually the results are merged when each GPU finishes its own process. The main advantage is to reduce the load on a single GPU by using lightweight Hough Matrices and output structures. Only CUDA implementation has been tested, using the same workload schema discussed in Sec. 3, but using four  $M_H(A, B, \theta)$ , each matrix processing the data of a single  $\phi$  sector.

#### 4.1 MULTI-GPU results

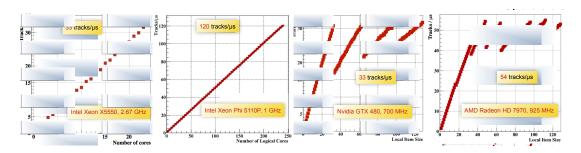

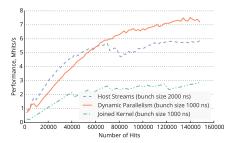

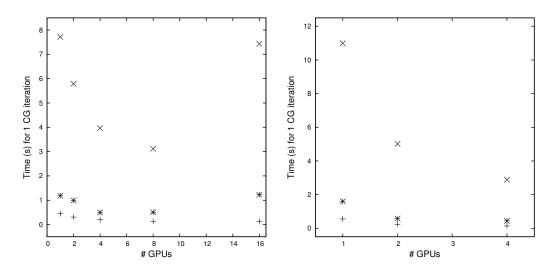

The multi-GPU results are shown in Fig. 4. The test has been carried out in double configuration, separately, with two NVIDIA Tesla K20 and two NVIDIA Tesla K40. The overall execution time is faster with double GPUs in both cases, even if timing does not scale with the number of GPUs. An approximate half timing is instead observed when comparing kernels execution times. On the other hand, the transferring time is almost independent on the number of GPUs, this leading the overall time execution.

Figure 3: Execution timing as a function of the number of analysed hits. (a) Total execution time for all devices; (b) Total execution time for GPU devices only; (c)  $M_H$  filling time for all devices; (d)  $M_H$  filling timing for GPU devices only; (e) local maxima search timing for all devices; (f) local maxima search timing for GPU devices only; (g) device-to-host transfer time (GPUS) and I/O time (CPU).

#### 5 Conclusions

A pattern recognition algorithm based on the Hough Transform has been successfully implemented on CUDA and OpenCL, also using multiple devices. The results presented in this paper show that the employment of GPUs in situations where time is critical for HEP, like triggering at hadron colliders, can lead to significant and encouraging speed-up. Indeed the problem by itself offers wide room for a parallel approach to computation: this is reflected in the results shown where the speed-up is around 15 times better than what achieved with a normal CPU. There are still many handles for optimising the performance, also taking into account the GPU architecture and board specifications. Next steps of this work go towards an interface to actual experimental frameworks, including the management of the experimental data structures and testing with more graphics accelerators and coprocessor.

#### References

- [1] NVidia Corporation URL http://www.nvidia.com/ NVidia Corporation URL http://www.nvidia.com/object/gpu.html NVidia Corporation URL http://www.nvidia.com/object/cuda\_home\_new.html

- [2] P. Hough; 1959 Proc. Int. Conf. High Energy Accelerators and Instrumentation C590914 554558

Figure 4: Execution timing as a function of the number of the hits for multi-GPU configuration. (a) Total execution time; (b)  $M_H$  filling timing; (c) local maxima search timing; (d) device-to-host transfer time.

- $[3]\,$  V Halyo et al; 2014 JINST  ${\bf 9}$  P04005

- M R Buckley, V Halyo, P Lujan; 2014 http://arxiv.org/abs/1405.2082

P. Hough, 1962, United States Patent 3069654.

- $[5]\,$  S Amerio et al; PoS (TIPP2014) 408

- [6] >> OpenCL,> Khronos>> Group>> URL>> https://www.khronos.org/opencl/

### FLES – First Level Event Selection Package for the CBM Experiment

Valentina Akishina<sup>1,2</sup>, Ivan Kisel<sup>1,2,3</sup>, Igor Kulakov<sup>1,3</sup>, Maksym Zyzak<sup>1,3</sup>

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/4

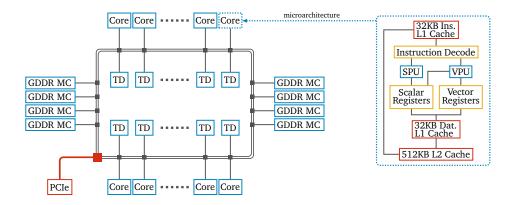

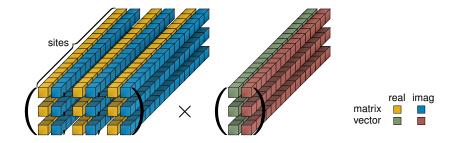

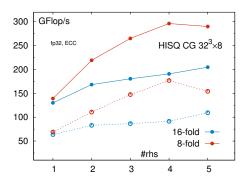

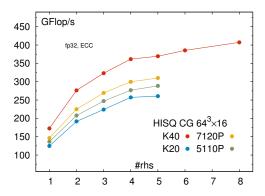

The CBM (Compressed Baryonic Matter) experiment is a future heavy-ion experiment at the future Facility for Anti-Proton and Ion Research (FAIR, Darmstadt, Germany). First Level Event Selection (FLES) in the CBM experiment will be performed on-line on a dedicated processor farm. An overview of the on-line FLES processor farm concept, different levels of parallel data processing down to the vectorization, implementation of the algorithms in single precision, memory optimization, scalability with respect to number of cores, efficiency, precision and speed of the FLES algorithms are presented and discussed.

#### 1 Introduction

The CBM (Compressed Baryonic Matter) experiment [1] is an experiment being prepared to operate at the future Facility for Anti-Proton and Ion Research (FAIR, Darmstadt, Germany). Its main focus is the measurement of very rare probes, that requires interaction rates of up to 10 MHz. Together with the high multiplicity of charged particles produced in heavy-ion collisions, this leads to huge data rates of up to 1 TB/s. Most trigger signatures are complex (short-lived particles, e.g. open charm decays) and require information from several detector sub-systems.

The First Level Event Selection (FLES) package [2] of the CBM experiment is intended to reconstruct the full event topology including tracks of charged particles and short-lived particles. The FLES package consists of several modules: track finder, track fitter, particle finder and physics selection. As an input the FLES package receives a simplified geometry of the tracking detectors and the hits, which are created by the charged particles crossing the detectors. Tracks of the charged particles are reconstructed by the Cellular Automaton (CA) track finder [3] using to the registered hits. The Kalman filter (KF) based track fit [4] is used for precise estimation of the track parameters. The short-lived particles, which decay before the tracking detectors, can be reconstructed via their decay products only. The KF Particle Finder, which is based on the KFParticle package [2], is used in order to find and reconstruct the parameters of short-lived particles by combining already found tracks of the long-lived charged particles. The KF Particle Finder also selects particle-candidates from a large number of random combinations. In addition, a module for quality assurance is implemented, that allows to control the quality of the reconstruction at all stages. It produces an output in a simple ASCII format, that can be

<sup>&</sup>lt;sup>1</sup>Goethe University, Grueneburgplatz 1, 60323 Frankfurt, Germany

<sup>&</sup>lt;sup>2</sup>FIAS Frankfurt Institute for Advanced Studies, Ruth-Moufang-Str. 1, 60438 Frankfurt, Germany

<sup>&</sup>lt;sup>3</sup>GSI Helmholtz Center for Heavy Ion Research, Planckstr. 1, 64291 Darmstadt, Germany

interpreted later as efficiencies and histograms using the ROOT framework. The FLES package is platform and operating system independent.

The FLES package in the CBM experiment will be performed on-line on a dedicated many-core CPU/GPU cluster. The FLES algorithms have to be therefore intrinsically local and parallel and thus require a fundamental redesign of the traditional approaches to event data processing in order to use the full potential of modern and future many-core CPU/GPU architectures. Massive hardware parallelization has to be adequately reflected in mathematical and computational optimization of the algorithms.

#### 2 Kalman Filter (KF) track fit library

Searching for rare interesting physics events, most of modern high energy physics experiments have to work under conditions of still growing input rates and regularly increasing track multiplicities and densities. High precision of the track parameters and their covariance matrices is a prerequisite for finding rare signal events among hundreds of thousands of background events. Such high precision is usually obtained by using the estimation algorithms based on the Kalman filter (KF) method. In our particular case, the KF method is a linear recursive method for finding the optimum estimation of the track parameters, grouped as components into the so-called state vector, and their covariance matrix according to the detector measurements.

The Kalman filter based library for track fitting includes following tracking algorithms: track fit based on the conventional Kalman filter; track fit based on the square root Kalman filter; track fit based on the Kalman filter with UD factorization of the covariance matrix; track smoother based on the listed above approaches and deterministic annealing filter based on the listed above track smoothers.

High speed of the reconstruction algorithms on modern many-core computer architectures can be accomplished by: optimizing with respect to the computer memory, in particular declaring all variables in single precision, vectorizing in order to use the SIMD (Single Instruction, Multiple Data) instruction set and parallelizing between cores within a compute node.

Several formulations of the Kalman filter method, such as the square root KF and the UD KF, increase its numerical stability in single precision. All algorithms, therefore, can be used either in double or in single precision.

The vectorization and parallelization of the algorithms are done by using of: header files, Vc vector classes, Intel TBB, OpenMP, Intel ArBB and OpenCL.

The KF library has been developed and tested within the simulation and reconstruction framework of the CBM experiment, where precision and speed of the reconstruction algorithms are extremely important.

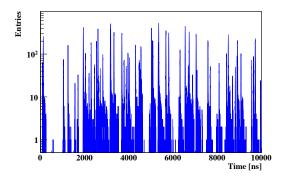

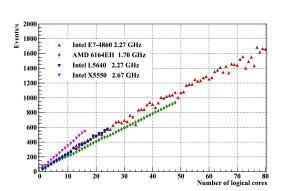

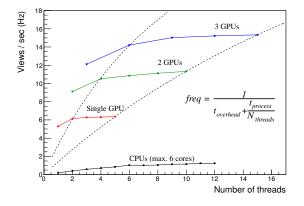

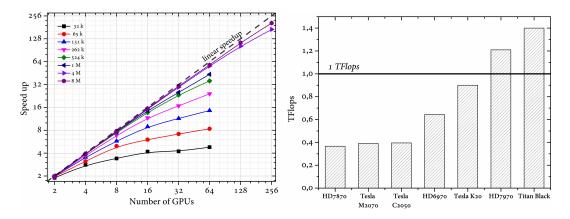

When running on CPU the scalability with respect to the number of cores is one of the most important parameters of the algorithm. Figure 1 shows the scalability of the vectorized KF algorithm. The strong linear behavior shows, that with further increase of the number of cores on newer CPUs the performance of the algorithm will not degrade and the maximum speed will be reached. The stair-like dependence appears because of the Intel Hyper-Threading technology, which allows to run two threads per core and gives about 30% of performance advantage. The scalability on the Intel Xeon Phi coprocessor is similar to CPU with four threads per core running simultaneously.

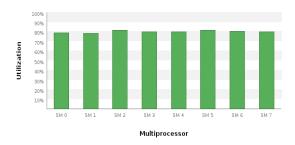

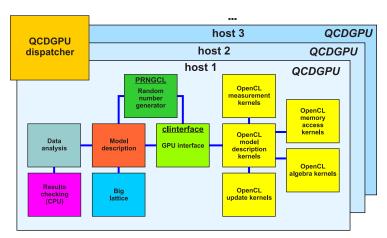

In case of the graphic cards the set of tasks is divided into working groups and distributed among compute units (or streaming multiprocessors) by OpenCL and the load of each compute

Figure 1: Portability of the Kalman filter track fit library on different many-core CPU/Phi/GPU architectures.

unit is of the particular importance. Each working group is assigned to one compute unit and should scale within it with respect to the number of tasks in the group. Figure 1 shows that the algorithm scales linearly on the graphic cards up to the number of cores in one compute unit (for Nvidia GTX480 — 32, for AMD Radeon HD 7970 — 16). Then the drop appears, because when first 32 (for Nvidia) or 16 (for AMD) tasks are processed, only one task is left and all other cores of the compute unit are idle. Increasing the number of tasks in the group further the speed reaches the maximum with the number of tasks dividable by the number of cores in the compute unit. Due to the overhead in tasks distribution the maximum performance is reached when the number of tasks in the group is two-three times more than the number of cores.

#### 3 Cellular Automaton (CA) track finder

Every track finder must handle a very specific and complicated combinatorial optimization process, grouping together one- or two-dimensional measurements into five-dimensional tracks.

In the Cellular Automaton (CA) method first (1) short track segments, so-called cells, are created. After that the method does not work with the hits any more but instead with the created track segments. It puts neighbor relations between the segments according to the track model here and then (2) one estimates for each segment its possible position on a track, introducing in such a way position counters for all segments. After this process a set of tree connections of possible track candidates appears. Then one starts with the segments with the largest position counters (3) and follows the continuous connection tree of neighbors to collect the track segments into track candidates. In the last step (4) one sorts the track candidates according to their length and  $\chi^2$ -values and then selects among them the best tracks.

The majority of signal tracks (decay products of D-mesons, charmonium, light vector mesons) are particles with momentum higher than 1 GeV/c originating from the region very close to the collision point. Their reconstruction efficiency is, therefore, similar to the efficiency of high-momentum primary tracks that is equal to 97.1%. The high-momentum secondary particles, e.g. in decays of  $K_s^0$  and  $\Lambda$  particles and cascade decays of  $\Xi$  and  $\Omega$ , are created far from the primary vertex, therefore their reconstruction efficiency is lower – 81.2%. Significant multiple scattering of low-momentum tracks in the material of the detector system and large curvature of their trajectories lead to lower reconstruction efficiencies of 90.4% for primary tracks and of 51.1% for secondary low-momentum tracks. The total efficiency for all tracks is

88.5% with a large fraction of low-momentum secondary tracks. The levels of clones (double found tracks) and of ghost (wrong) tracks are 0.2% and 0.7% respectively. The reconstruction efficiency of the CA track finder is stable with respect to the track multiplicity.

The high track finding efficiency and the track fit quality are crucial, especially for reconstruction of the short-lived particles, which are of the particular interest for the CBM experiment. The reconstruction efficiency of short-lived particles depends quadratically on the daughter track reconstruction efficiency in case of two-particle decays. The situation becomes more sensitive for decays with three daughters and for decay chains. The level of a combinatorial background for short-lived particles depends strongly on the track fit quality. The correct estimation of the errors on the track parameters improves distinguishing between the signal and the background particle candidates, and thus to suppress the background. The ghost (wrong) tracks usually have large errors on the track parameters and therefore are easily combined with other tracks into short-lived particle candidates, thus a low level of ghost tracks is also important to keep the combinatorial background low. As a result, the high track reconstruction efficiency and the low level of the combinatorial background improve significantly the event reconstruction and selection by the FLES package.

#### 4 4-Dimensional time-based event building

Since resolving different events is a non-trivial task in the CBM experiment, the standard reconstruction routine will include an event building, the process of defining exact borders of events within a time-slice and grouping tracks into even-corresponding clusters, which they originate from. For this task an efficient time-based tracking is essential. Since the CA track finder is proved to be fast and stable with respect to the track multiplicity, the next step towards the time-slice based reconstruction would be the implementation of time measurements.

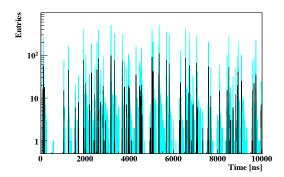

Figure 2: Part of a time-slice with 100 minimum bias events. With blue color the distribution of hit time measurements in a time-slice is shown.

Figure 3: Part of a time-slice with 100 minimum bias events. With light blue color the initial distribution of hit measurements is reproduced, black color shows time measurements of reconstructed tracks.

In order to introduce a time measurement into the reconstruction procedure to each minimum bias event in a 100 events group an event start time was assigned during simulation phase. The start time was obtained with the Poisson distribution, assuming the interaction

rate of 10<sup>7</sup> Hz. A time stamp we assign to a certain hit consists of this event start time plus the time shift due to the time of flight, which is different for all hits. In order to obtain a time measurement for a hit we then smear a time stamp according to a Gaussian distribution with a sigma value of the detector resolution of 5 ns.

After introducing the time measurement we can use the time information in the CA track finder. We do not allow to build triplets out of hits, which time difference is greater than  $3\sigma$  of the detector time resolution. It is a very good approximation, since the time of flight between the detector planes is negligible in comparison to the detection precision. Apart from that, we perform the reconstruction procedure in a regular way. After the reconstruction we assign to each track a time measurement, which is calculated as an average of its hits measurements.

The initial distribution of hits measurements representing the complexity of defining event borders in a time-slice at interaction rate of 10<sup>7</sup> Hz is shown in Fig. 2 with blue color. The resulting distribution of reconstructed track measurements (black color), as well as the distribution of initial hit measurements (light blue color), one can see in Fig. 3. The reconstructed tracks clearly represent groups, which correspond to events, which they originate from.

# 5 KF Particle Finder – a package for reconstruction of short-lived particles

Today the most interesting physics is hidden in the properties of short-lived particles, which are not registered, but can be reconstructed only from their decay products. A fast and efficient KF Particle Finder package, based on the Kalman filter (hence KF) method, for reconstruction and selection of short-lived particles is developed to solve this task. A search of more than 50 decay channels has been currently implemented.

In the package all registered particle trajectories are divided into groups of secondary and primary tracks for further processing. Primary tracks are those, which are produced directly in the collision point. Tracks from decays of resonances (strange, multi-strange and charmed resonances, light vector mesons, charmonium) are also considered as primaries, since they are produced directly at the point of the primary collision. Secondary tracks are produced by the short-lived particles, which decay not in the point of the primary collision and can be clearly separated. These particles include strange particles  $(K_s^0 \text{ and } \Lambda)$ , multi-strange hyperons ( $\Xi$  and  $\Omega$ ) and charmed particles  $(D_0, D^{\pm}, D_s^{\pm} \text{ and } \Lambda_c)$ . The package estimates the particle parameters, such as decay point, momentum, energy, mass, decay length and lifetime, together with their errors. The package has a rich functionality, including particle transport, calculation of a distance to a point or another particle, calculation of a deviation from a point or another particle, constraints on mass, decay length and production point. All particles produced in the collision are reconstructed at once, that makes the algorithm local with respect to the data and therefore extremely fast.

KF Particle Finder shows a high efficiency of particle reconstruction. For example, for the CBM experiment efficiencies of about 15% for  $\Lambda$  and 5% for  $\Xi^-$  with AuAu collisions at 35 AGeV are achieved together with high signal-to-background ratios (1.3 and 5.9 respectively).

#### 6 A standalone FLES package for the CBM experiment

The First Level Event Selection (FLES) package of the CBM experiment is intended to reconstruct on-line the full event topology including tracks of charged particles and short-lived particles. The FLES package consists of several modules: CA track finder, KF track fitter, KF Particle Finder and physics selection. In addition, a quality check module is implemented, that allows to monitor and control the reconstruction process at all stages. The FLES package is platform and operating system independent.

The FLES package is portable to different many-core CPU architectures. The package is vectorized using SIMD instructions and parallelized between CPU cores. All algorithms are optimized with respect to the memory usage and the speed.

0 10 20 30 40 50 60 70 80 90

250

A AMD Opteron 6272, 2.1 GHz

2.2×10<sup>5</sup> events/s

150

50

50

50

100

2000

2500

3000

3000

Number of Cores

Figure 4: Scalability of the FLES package on many-core servers with 16, 24, 48 and 80 logical cores.

Figure 5: Scalability of the FLES package on 3 200 cores of the FAIR-Russia HPC cluster (ITEP, Moscow).

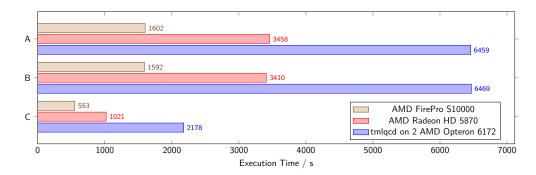

Four servers with Intel Xeon X5550, L5640 and E7-4860 processors and with AMD 6164EH processor have been used for the scalability tests. The AMD server has 4 processors with 12 physical cores each, in total 48 cores. All Intel processors have the hyper-threading technology, therefore each physical core has two logical cores. The Intel X5550 and L5640 servers with two CPUs each have in total 16 and 24 logical cores respectively. The most powerful Intel server has 4 processors E7-4860 with 10 physical cores each, that gives 80 logical cores in total.

The FLES package has been parallelized with ITBB (Intel Threading Building Blocks) implementing the event-level parallelism by executing one thread per one logical core. Reconstruction of 1000 minimum bias Au-Au UrQMD (Ultrarelativistic Quantum Molecular Dynamics model) events at 25 AGeV has been processed per each thread. In order to minimize the effect of the operating system each thread is fixed to a certain core using the pthread functionality provided by the C++ standard library. Fig. 4 shows a strong scalability for all many-core systems achieving the reconstruction speed of 1700 events per second on the 80-cores server.

The FLES package in the CBM experiment will be performed for the on-line selection and the off-line analysis on a dedicated many-core CPU/GPU farm. The farm is currently estimated to have a compute power equivalent to 60 000 modern CPU cores. Fig. 5 shows the scalability of the FLES package on a many-core computer farm with 3 200 cores of the FAIR-Russia HPC cluster (ITEP, Moscow).

#### 7 Summary

The standalone FLES package has been developed for the CBM experiment. It contains track finding, track fitting, short-lived particles finding and physics selection. The Cellular Automaton and the Kalman filter algorithms are used for finding and fitting tracks, that allows to achieve a high track reconstruction efficiency. The event-based CA track finder was adapted for the time-based reconstruction, which is a requirement in the CBM experiment for the event building. The 4D CA track finder allows to resolve hits from different events overlapping in time into event-corresponding clusters of tracks. Reconstruction of about 50 decay channels of short-lived particles is currently implemented in the KF Particle Finder. The package shows a high reconstruction efficiency with an optimal signal to background ratio.

The FLES package is portable to different many-core CPU architectures. The package is vectorized and parallelized. All algorithms are optimized with respect to the memory usage and the processing speed. The FLES package shows a strong scalability on the many-core CPU systems and the processing and selection speed of 1700 events per second on a server with 80 Intel cores. On a computer cluster with 3 200 AMD cores it processes up to  $2.2 \cdot 10^5$  events per second.

#### References

- [1] The CBM Collaboration, Compressed Baryonic Matter Experiment, Tech. Stat. Rep., GSI, Darmstadt, 2005; 2006 update

- [2] I. Kisel, I. Kulakov and M. Zyzak, IEEE Trans. Nucl. Sci. 60, 3703–3708 (2013)

- [3] I. Kisel, Nucl. Instr. and Meth. **A566** 85–88 (2006)

- [4] S. Gorbunov, U. Kebschull, I. Kisel, V. Lindenstruth, and W.F.J. Müller, Comp. Phys. Comm., 178, 374–383 (2008)

# Tree Contraction, Connected Components, Minimum Spanning Trees: a GPU Path to Vertex Fitting

Raul H. C. Lopes<sup>1</sup>, Ivan D. Reid<sup>1</sup>, Peter R. Hobson<sup>1</sup>

<sup>1</sup>Department of Electronic & Computer Engineering, Brunel University London, Kingston Lane, Uxbridge, UB8 3PH, United Kingdom

**DOI:** http://dx.doi.org/10.3204/DESY-PROC-2014-05/5

Standard parallel computing operations are considered in the context of algorithms for solving 3D graph problems which have applications, e.g., in vertex finding in HEP. Exploiting GPUs for tree-accumulation and graph algorithms is challenging: GPUs offer extreme computational power and high memory-access bandwidth, combined with a model of fine-grained parallelism perhaps not suiting the irregular distribution of linked representations of graph data structures. Achieving data-race free computations may demand serialization through atomic transactions, inevitably producing poor parallel performance. A Minimum Spanning Tree algorithm for GPUs is presented, its implementation discussed, and its efficiency evaluated on GPU and multicore architectures.

#### 1 Introduction

We are concerned with the problem of finding parallel algorithms to compute a Minimum Spanning Tree for a weighted undirected graph. We introduce a parallel algorithm for computing minimum spanning trees over weighted undirected graphs.

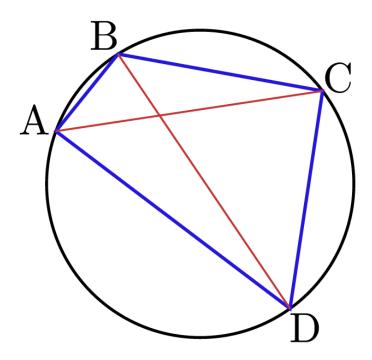

An undirected graph G is a pair (V, E), where V is a finite nonempty set of vertices and E is a set of unordered pairs of vertices in V, called the set of edges of G. A path in G is a sequence of edges  $e_0, e_1, \ldots, e_n$ , with  $e_i$  and  $e_{i+1}$ , for  $i \in \{0..n-1\}$ , sharing exactly one vertex. A cycle is path  $e_0, e_1, \ldots, e_n$ , where  $e_0$  and  $e_n$  share one vertex. A graph G is connected if there is a path between any pair of its vertices. A tree is connected graph containing no cycles. A spanning tree for a graph G is a tree containing all vertices in G. A spanning forest for a graph G that is not connected is a set of spanning trees, one for each connected component of G. A graph G is weighted when a function G0 as weights to each edge of G1. A graph's weight is the sum of weights of its edges. A Minimum Spanning Tree (MST) of a graph G1 is a tree of minimal weight among all spanning trees of G2. The concept extends to that of Minimum Spanning Forest (MSF) of G2 as a spanning forest of minimum weight.

Throughout this paper we will use n to denote number of vertices in a graph G, and m to denote its number of edges. An MST in  $\mathbb{R}^2$  can be computed in  $O(n \lg n)$  using Delaunay triangulations. However, the work demanded to compute an MST in  $\mathbb{R}^d$  is limited from below by  $\Omega(m)$  when d > 2, see [1]. Even the representation in memory of the edges of a  $2^{20}$  vertices graph could be a challenge.

Minimum spanning trees have applications, for example, in computer networks, water supply networks, and electrical grids. The computation of MSTs is considered a fundamental challenge in Combinatorial Optimization [2] and is of interest for the HEP community.

In the next sections, we discuss first sequential algorithms for computing connected and spanning trees, and the difficulties involved in parallelizing them. Then we present an algorithm for computing minimum spanning trees on GPU architectures and discuss its performance on both GPU and multi-core architectures.

#### 2 Sequential Algorithms

Minimum spanning tree computations make use of the following property to choose edges from the underlying graph to add to its MST. See [3] for a proof of its soundness.

Cut property: The lightest edge connecting any nonempty subset X of V(G) to V(G) - X belongs to MSF(G).

The Borŭvka algorithm is historically the first and possibly most general MSF algorithm. It uses the cut property to maintain the following invariant: each tree in the forest is an MST for the vertices in it, and each vertex in the initial graph belongs to exactly one tree. It starts with a set of forests, each containing exactly one vertex from the given graph G. Borŭvka's is essentially a non-deterministic algorithm in which, at any time, all lightest edges that can expand any of its trees can be added. It's important to notice, however, that each edge addition joins two trees and this must be reflected in the data structures used in its implementation. Also, its non-deterministic nature appeals to parallel implementations, but introduces possible data-race conditions.

Most theoretically efficient MST algorithms use Borŭvka functions, as for example [4], and the deterministic algorithm given by [1] and [5]. These algorithms, however, seem to lack efficient practical implementations or parallel versions. The most successful implementations of sequential MST algorithms, the **Prim-Dijkstra** and **Kruskal** algorithms evaluated in [6], can be seen as specializations of the Borŭvka algorithm and they also maintain an invariant, see [7], where at any moment in the computation the edges already selected by the algorithm form an MST of the subgraph in question and any new edge added satisfies the *cut property*. In particular the Kruskal algorithm [3] is a sequential version of the Borŭvka algorithm where edges are processed in increasing order of weights.

In the next section, we discuss the challenges found in parallelizing the Borŭvka algorithm and the fundamental requirements for parallelization of a minimum spanning tree computation.

#### 3 Parallel Algorithms

The nondeterministic nature of Borŭvka's algorithm clearly invites the introduction of asynchronous parallelism in its implementation. We would have an algorithm that performs a sequence of parallel steps, where each parallel step joins all possible pairs of trees, using the lightest edges connecting them. However, care must be taken in that: more than two trees may be joined in the same parallel step; given two trees  $t_0$  and  $t_1$  joined in a parallel step, all edges connecting vertices in  $t_0$  to vertices in  $t_1$  must be discarded.

Those problems result from the fact that many trees may be expanded simultaneously. The Prim-Dijkstra algorithm expands exactly one tree and thus avoids complications of performing simultaneous unions of vertices and edges by being strictly sequential. The **Kruskal** algorithm

excludes the possibility of joining more than two trees simultaneously by processing the edges in increasing order of weight. It still keeps track of more than one tree being expanded at any time, but each expansion and join is serialized. Its first obvious disadvantage is in processing the edges in increasing weight order, which demands ordering all edges before the real construction of the tree starts, which can be very expensive or even prohibitive when processing, for example, Euclidean graphs where the number of edges can approach  $n^2$ . A graph with  $2^{20}$  vertices might demand memory to maintain close to  $2^{40}$  edges, maybe two to four terabytes just to store edge weights.

The Kruskal algorithm, or any other derived from the Borŭvka algorithm, must still take care of the joining of trees and the union of sets of respective vertices and edges. In practice this is performed using efficient implementations of the disjoint-set data structure, see [8]. A disjoint-set data structure offers fast union of two sets by labeling the elements of two sets with a common identifier that defines that new common set that they belong to. It offers fast set membership tests by performing a fast search from the vertex to the label of the structure representing the set it belongs to. In a sequential implementation this is achieving by making vertices the leaves of trees where each node points to its parent, with the root of the tree pointing to itself and being taken as the label of the tree. Set union is trivially performed by making the root of one tree to point to the root of another tree. However, this is an operation that must be synchronized. Synchronization may also be needed if the search for a tree's root is performed concurrently with a join operation.

Nondeterminism has been forcefully defended by authors like Dijkstra [9] and Lamport [10] as a powerful tool in the design of computer algorithms and concurrent systems. More recently, Steele [11] has made a strong point for the integration of asynchronous computations in synchronous parallel algorithms, given that asynchronous programs tend to be more flexible and efficient when processing conditionals. In addition many authors have pointed out asynchronous and non-deterministic parallelism as the root of success of many programs based on the MapReduce model [12].

An ideal implementation of Borŭvka's algorithm would start as many asynchronous threads as possible, each expanding a different minimum spanning tree. Synchronization, however, would be needed, for example, if a tree  $t_0$  must be joined to a tree  $t_1$  while, simultaneously,  $t_1$  is being joined to  $t_2$  and  $t_2$  is being joined with  $t_0$ . That sort of synchronism is a fundamental requirement of any parallel implementation of Borŭvka's algorithm.

The objective of this paper is to present a GPU algorithm. Its design must take into account that GPU architectures perform at their peak when running in SIMD (Single-Instruction-Multiple-Data) fashion. Performance is lost when atomic transactions, or conditions that send threads into different paths, are present.