Internal Report DESY F35D-93-02 January 1993

# The Study on the Radiation Sensitivity of the MOS Transistors for Application in the Front-End VLSI Electronics of ZEUS Detector

by

A. Skoczeń

| Eigentum<br>Property | der DESV      | il-hothek<br>literary |

|----------------------|---------------|-----------------------|

| Zugan                | - 1, MRZ, 199 | 13                    |

| Leh al<br>Lonn de    | ice I         |                       |

DESY behält sich alle Rechte für den Fall der Schutzrechtserteilung und für die wirtschaftliche Verwertung der in diesem Bericht enthaltenen Informationen vor.

DESY reserves all rights for commercial use of information included in this report, especially in case of filing application for or grant of patents.

"Die Verantwortung für den Inhalt dieses Internen Berichtes liegt ausschließlich beim Verfasser" Internal Report DESY F35D-93-02 January 1993

# The Study on the Radiation Sensitivity of the MOS Transistors for Application in the Front-End VLSI Electronics of ZEUS Detector

by

A. Skoczeń

.

The Study on the Radiation Sensitivity of the MOS Transistors for Application in the Front-End VLSI Electronics of ZEUS Detector.

This doctoral dissertation is to be presented at the Faculty of Physics and Nuclear Technique, Academy of Mining and Metallurgy in Cracow.

The work described in this thesis has been carried out at the Deutsches Elektronen-Synchrotron, DESY in Hamburg in the frame of collaboration with ZEUS. Over the period of his stay at DESY the author was financially supported by DESY.

Andrzej Skoczeń

ACADEMY OF MINING AND METALLURGY Cracow Faculty of Physics and Nuclear Technique Department of Nuclear Electronics

28 January 1993

# Contents

- -

.....

| L | ist o | f symbols                                                           | 3   |

|---|-------|---------------------------------------------------------------------|-----|

| 1 | Int   | roduction                                                           | 9   |

| 2 | Ide   | al and nonideal MOS structure                                       | 13  |

|   | 2.1   | Definitions of MOS transistor parameters                            | 19  |

|   |       | 2.1.1 A theoretical definition of threshold voltage                 | 19  |

|   |       | 2.1.2 Transconductance                                              | 22  |

|   |       | 2.1.3 Drain conductance                                             | 24  |

|   |       | 2.1.4 Subthreshold swing                                            | 25  |

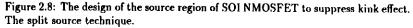

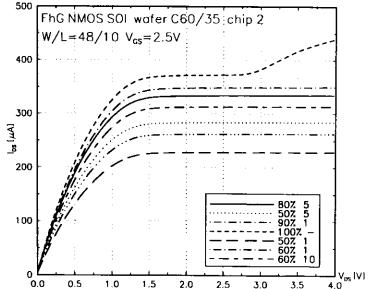

|   |       | 2.1.5 Kink effect                                                   | 26  |

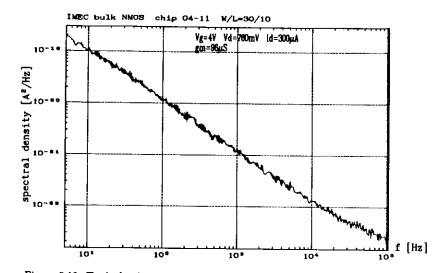

|   |       | 2.1.6 Spectral noise power density                                  | 29  |

| 3 | Tec   | hnologi <del>es</del>                                               | 33  |

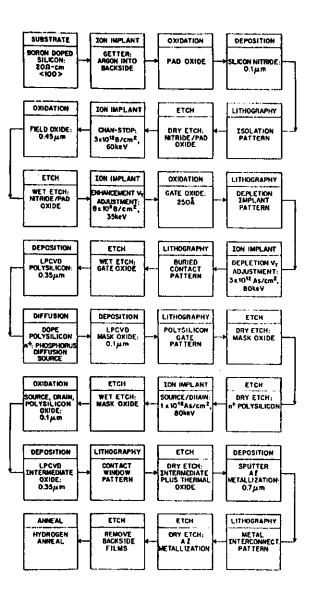

|   | 3.1   | Bulk technology                                                     | 34  |

|   | 3.2   | SOI technology                                                      | 39  |

|   | 3.3   | Radiation hardened technology                                       | 45  |

|   |       | 3.3.1 Technological considerations                                  | 45  |

|   |       | 3.3.2 Layout considerations                                         | 54  |

| 4 | Th    | eshold voltage shift and transconductance degradation               | 63  |

|   | 4.1   | Mechanisms and processes leading to degradation                     | 64  |

|   | 4.2   | Threshold voltage and transconductance extraction methods           | 66  |

|   | 4.3   | The influence of radiation generated charges on transconductance    | 68  |

|   | 4.4   | The influence of radiation generated charges on threshold voltage   | 69  |

|   | 4.5   | The methods for separating the effects of interface traps and oxide | 00  |

|   |       | charges                                                             | 71  |

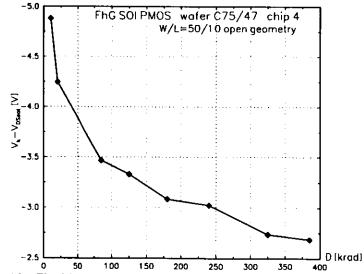

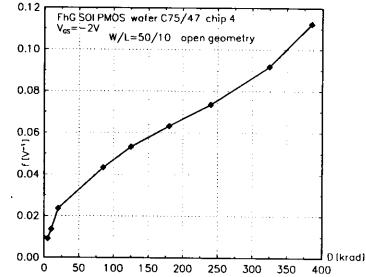

|   | 4.6   | The results for SOI transistors and discussion                      | 79  |

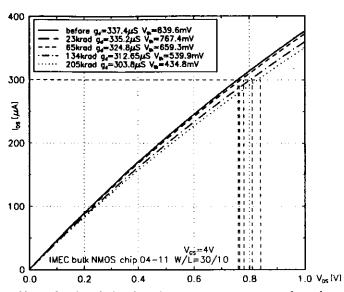

|   | 4.7   | The influence of radiation on the kink effect                       | 93  |

| 5 |       | ker noise                                                           | 101 |

|   | 5.1   | Models for flicker noise in MOSFETs                                 | 102 |

|   |       | 5.1.1 The number-fluctuation model                                  | 103 |

|   |       | 5.1.2 The mobility-fluctuation model                                | 107 |

|   |       | 5.1.3 The unified model                                             | 109 |

|   | 5.2   | Noise measurement                                                   | 110 |

1

2

### CONTENTS

.

|    | 5.3   | Radiation influence on flicker noise                 | 112 |

|----|-------|------------------------------------------------------|-----|

|    | 5.4   | Kink effect in noise and its dependence on radiation | 118 |

| 6  | Con   | clusion                                              | 123 |

| A  | The   | approximate model for the strong inversion region    | 127 |

| B  | The   | model for the weak inversion region                  | 131 |

| С  | The   | Langevin method of $S_x(f)$ evaluation               | 135 |

| Bi | bliog | raphy                                                | 136 |

| Su | mma   | ary                                                  | 146 |

| St | reszc | zenie                                                | 149 |

| Ac | know  | vledgements                                          | 153 |

# List of symbols

| a                       | Slope of a straight line (obtained from linear regression method).                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|

| Ä                       | Constant in the formula for $1/f$ noise                                                                         |

| Ao                      | Open loop gain.                                                                                                 |

| A,                      | Ionization constant.                                                                                            |

| an                      | Amplitude of <i>n</i> -th term of Fourier's series $(\equiv \frac{1}{T} \int_0^T x(t) \exp(-j\omega_n t) dt)$ . |

| Α̈́(τ)                  | Autocorrelation function of the voltage fluctuation.                                                            |

| α                       | Sun-Plummer parameter.                                                                                          |

| a*                      | Relative Sun-Plummer parameter ( $\equiv \alpha \frac{\Delta N_{ii}}{\Delta V_{ii}}$ ).                         |

| $\alpha(\mathcal{E}_h)$ | Ionization rate for the weak impact ionization $(\equiv A_i \exp(-\frac{B_i}{\xi_i}))$ .                        |

| α <sub>H</sub>          | Hooge's constant.                                                                                               |

| αHI                     | Hooge's constant for 1/f noise in lattice scattering.                                                           |

| Ь                       | y-intercept of straight line (obtained from linear regression method).                                          |

| b <sub>n</sub>          | Amplitude of n-th term of Fourier's series.                                                                     |

| Bi                      | lonization constant.                                                                                            |

| ß                       | Transconductance or gain factor $(\equiv \mu_n C_{ox} \frac{W}{L})$ .                                           |

| С                       | Constant.                                                                                                       |

| С <sub>В</sub>          | Constant impurity concentration deep in the substrate.                                                          |

| $C_D$                   | Depletion region capacitance.                                                                                   |

| Ceff                    | Effective gate capacitance.                                                                                     |

| Cinv                    | Inversion layer capacitance.                                                                                    |

| $C_{it}$                | Interface states capacitance.                                                                                   |

| Coz                     | Gate oxide capacitance $(\equiv \frac{\epsilon_{S1O_2}\epsilon_0}{t_{ox}})$ .                                   |

| x                       | Electron affinity in silicon ( $\equiv E_0 - E_C^{Si}$ ).                                                       |

| D                       | Radiation dose.                                                                                                 |

| Dbe                     | Density of border states per unit area per eV.                                                                  |

| D <sub>it</sub>         | Density of interface states per unit area per eV.                                                               |

| D <sub>itA</sub>        | Density of acceptor interface states.                                                                           |

| D <sub>itD</sub>        | Density of donor interface states.                                                                              |

| $D_{n,p}$               | Diffusion constant; the index n denotes the electrons in NMOSFET and                                            |

|                         | $p$ - holes in PMOSFET ( $\equiv \mu_n V_t$ , Einstein's relation).                                             |

| D <sub>ot</sub>         | Density of oxide states per unit area per eV.                                                                   |

| d(7)                    | Distribution of the border traps with respect to the time constant $\tau$ .                                     |

| 8                       | Inversion layer thickness.                                                                                      |

| δ                       | Factor of the first order correction in the Taylor's expansion of the                                           |

| <u>.</u>                | depletion region charge.                                                                                        |

| $\delta V_{\mu}$        | Voltage fluctuation due to mobility fluctuation.                                                                |

| $\delta V_n$            | Voltage fluctuation due to carrier number fluctuation.                                                          |

| δX                                                                          | Electuation of quantity $Y$ (for exercise $Y = N - I$ )                                                                                                                                                             |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Delta X$                                                                  | Fluctuation of quantity X (for example $X = N_t, I_{DS},$ ).                                                                                                                                                        |

| Ē                                                                           | Change of quantity X (for example $X = V_{th}, V_{ot}, N_{ot},)$ .                                                                                                                                                  |

| E                                                                           | Energy of the carriers in the silicon or in the oxide.                                                                                                                                                              |

|                                                                             | Energy of the ionizing radiation.                                                                                                                                                                                   |

| E0<br>E0F                                                                   | Energy of vacuum level.                                                                                                                                                                                             |

| E <sub>C</sub>                                                              | Oxide conduction band edge.                                                                                                                                                                                         |

| E₀<br>E°<br>E <sup>Si</sup><br>E <sup>Si</sup><br>E <sub>€</sub>            | Silicon conduction band edge.                                                                                                                                                                                       |

| Ľ,                                                                          | Average energy of secondary electrons created by Compton scattering                                                                                                                                                 |

| _                                                                           | of the photons.                                                                                                                                                                                                     |

| E <sub>F</sub>                                                              | Fermi energy level.                                                                                                                                                                                                 |

| E <sub>FM</sub>                                                             | Energy of metal Fermi level.                                                                                                                                                                                        |

| $E_{F_n}$                                                                   | Electron quasi-Fermi level.                                                                                                                                                                                         |

| E <sub>g</sub>                                                              | Silicon bandgap energy.                                                                                                                                                                                             |

| $E_{g}^{ox}$                                                                | Oxide bandgap energy.                                                                                                                                                                                               |

| $E_i$                                                                       | Intrinsic energy level.                                                                                                                                                                                             |

| $E_g$<br>$E_g^{ox}$<br>$E_i$<br>$E_V^{ox}$<br>$E_V^{Si}$<br>$\mathcal{E}_h$ | Oxide valence band edge.                                                                                                                                                                                            |

| $E_V^{Si}$                                                                  | Silicon valence band edge.                                                                                                                                                                                          |

| $\mathcal{E}_h$                                                             | Horizontal channel field.                                                                                                                                                                                           |

| $\mathcal{E}_{hd}$                                                          | Horizontal electric field in the drain space charge region.                                                                                                                                                         |

| Eh.                                                                         | Critical horizontal field for the velocity saturation.                                                                                                                                                              |

| ε,                                                                          | Normal electric field at the silicon surface.                                                                                                                                                                       |

| $\mathcal{E}_{crit}$                                                        | Critical normal field.                                                                                                                                                                                              |

| Eeff                                                                        | Effective normal field.                                                                                                                                                                                             |

| Eor                                                                         | Effective normal field in the oxide.                                                                                                                                                                                |

| £                                                                           | Characteristic trapping distance into the oxide.                                                                                                                                                                    |

| Eau                                                                         | Average dielectric constant of Si and $SiO_2$ ( $\equiv \frac{1}{2}(\varepsilon_{Si} + \varepsilon_{SiO_2})$ ).                                                                                                     |

| εo                                                                          | Permittivity of free space.                                                                                                                                                                                         |

| Esi                                                                         | Dielectric constant of silicon.                                                                                                                                                                                     |

| ESiO2                                                                       | Dielectric constant of silicon dioxide.                                                                                                                                                                             |

| $\eta_{n,p}$                                                                | Relative mobility degradation ( $\equiv \frac{\mu_{n,p} \text{ before} - \mu_{n,p} \text{ after}}{\mu_{n,p} \text{ after}}$ ); the index <i>n</i> denotes the electrons in NMOSFET and <i>p</i> - holes in PMOSFET. |

|                                                                             | tes the electrons in NMOSFET and $p$ - holes in PMOSFET.                                                                                                                                                            |

| <u>4E</u><br>4 <del>.</del>                                                 | Stopping power.                                                                                                                                                                                                     |

| <u>4E</u><br>41<br>∫                                                        | Frequency.                                                                                                                                                                                                          |

| ſ                                                                           | Kink effect parameter.                                                                                                                                                                                              |

| fo                                                                          | Open loop cut-off frequency.                                                                                                                                                                                        |

| $F_A(\psi)$                                                                 | Fermi-Dirac distribution for acceptors.                                                                                                                                                                             |

| $F_D(\psi)$                                                                 | Fermi-Dirac distribution for donors.                                                                                                                                                                                |

| fh                                                                          | High limit frequency.                                                                                                                                                                                               |

| -<br>fi                                                                     | Low limit frequency.                                                                                                                                                                                                |

| Ĵ.                                                                          | Fractional occupancy.                                                                                                                                                                                               |

| Ĵ <sub>T</sub>                                                              | Fraction of the radiation-induced holes which are trapped in the oxide.                                                                                                                                             |

| $f(\psi_s)$                                                                 | Function used for short notation the accurate equation modelling the                                                                                                                                                |

|                                                                             | MOS transistor characteristic in the strong inversion region.                                                                                                                                                       |

| $\phi_B$                                                                    | Fermi energy level measured with respect to the midgap level deep in                                                                                                                                                |

|                                                                             | the substrate (under depletion region where the bands are not bended).                                                                                                                                              |

| $\phi_G$                                                                    | (similar to $\phi_B$ but for polysilicon gate electrode, $(\equiv V_i \ln \frac{N_{BATE}}{T_i})$ .                                                                                                                  |

|                                                                             | $n_1$                                                                                                                                                                                                               |

| $\Phi_{GB}$           | Difference between the work functions of all an autotate and a task                                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • 68                  | Difference between the work functions of silicon substrate and gate elec-                                                                                                               |

| Φ <sub>M</sub>        | trode material.<br>Work function of metal $(-E - E)$                                                                                                                                    |

| $\Phi_{SC}$           | Work function of metal ( $\equiv E_0 - E_{FM}$ ).<br>Work function of cilicon                                                                                                           |

| G                     | Work function of silicon.<br>Conductance.                                                                                                                                               |

| $g(N_t)$              |                                                                                                                                                                                         |

| g(m) = g(1/)          | Function describing the generation of carriers.                                                                                                                                         |

| y(y) = y(y)           | Conductance per unit length of the channel at the distance y from                                                                                                                       |

|                       | source.                                                                                                                                                                                 |

| g <sub>d</sub>        | Drain conductance.                                                                                                                                                                      |

| g <sub>m</sub>        | Transconductance.                                                                                                                                                                       |

| 7                     | Body effect coefficient (= $\frac{\sqrt{2\epsilon_{S_i}\epsilon_0 qN_A}}{C_{os}}$ ).                                                                                                    |

| γ<br>h                | Frequency exponent.                                                                                                                                                                     |

| л<br>ћ                | Plank's constant.                                                                                                                                                                       |

| h(t)                  | Plank's constant $(\equiv \frac{h}{2\pi})$ .                                                                                                                                            |

| n(t)                  | Noise extortion.<br>1 Current.                                                                                                                                                          |

| IBS                   |                                                                                                                                                                                         |

| 185<br>1 <sub>d</sub> | Current through the source-to-body diode.                                                                                                                                               |

| I <sub>DB</sub>       | Instantaneous value of the current noise of transistor channel.                                                                                                                         |

|                       | Current through the drain-to-body diode.<br>Drain current.                                                                                                                              |

| I <sub>DSmax</sub>    | Maximal drain current at fixed rate voltage in the subthers hall                                                                                                                        |

| Domas                 | $(= AC_{-}(h) P V_{2}^{2} \exp(\frac{V_{0S} - V_{0S}^{*}}))$                                                                                                                            |

| IDSeal                | Maximal drain current at fixed gate voltage in the subthreshold range $(\equiv \beta C_D(\psi_a) \frac{n}{m} V_i^2 \exp(\frac{V_{GS} - V_{GS}^2}{nV_i})).$<br>Saturation drain current. |

|                       | Impact ionization current.                                                                                                                                                              |

|                       | Midgap current $(\psi_s = \phi_B)$ .                                                                                                                                                    |

| 2 m g                 | Instantaneous value of the current input noise of amplifier.                                                                                                                            |

| Is                    | Current measured in the source of the transistor.                                                                                                                                       |

| Ith                   | Threshold current $(\psi_s = 2\phi_B)$ .                                                                                                                                                |

| ITR                   | Current through the front transistor channel.                                                                                                                                           |

| I.w                   | Current measured in the n-well.                                                                                                                                                         |

| k                     | Boltzman's constant.                                                                                                                                                                    |

| K                     | Constant $(\equiv V_t^2 \exp(-\frac{2\phi_B}{V_t})[1 - \exp(-\frac{V_{DS}}{V_t})])$ .                                                                                                   |

| К                     | Noise level of the drain current flicker noise.                                                                                                                                         |

| K <sub>v</sub>        | Noise level normalized with respect to the drain $V_{DS}$ and threshold $V_{th}$                                                                                                        |

|                       | $voltages (\equiv KR^2 \left(\frac{V_{GS} - V_{IA} - V_{OS}}{V_{DS}}\right)^2).$                                                                                                        |

| κ                     | $(= m V_{DS})$                                                                                                                                                                          |

| Ĺ                     | $(\equiv \frac{m}{n} \frac{V_{DS}}{V_i}).$<br>Nominal gate length.                                                                                                                      |

| LR                    | Extrinsic Dobase longth (m. /sservi)                                                                                                                                                    |

|                       | Extrinsic Debeye length ( $\equiv \sqrt{\frac{e_{Srep}V_1}{qN_A}}$ ).                                                                                                                   |

| L.                    | Pinch-off point distance from source.                                                                                                                                                   |

| $L_{eff}$<br>$L^m(p)$ | Effective gate length.                                                                                                                                                                  |

| $\lambda$             | Polynomial of m-degree.                                                                                                                                                                 |

| λ                     | Characteristic length of hole trapping process.                                                                                                                                         |

| λ                     | Mean separation between e-h pairs.                                                                                                                                                      |

|                       | Characteristic length for channel length modulation.                                                                                                                                    |

| λ <sub>eff</sub>      | Encourse mean free path.<br>$C_{m} + C_{n}(\frac{2}{2}\phi_{n})$                                                                                                                        |

| m<br>Az               | Effective mean free path.<br>$ (\equiv \frac{C_{out} + C_D(\frac{3}{2} \neq B)}{C_{out}}). $ Multiplication factor.                                                                     |

| М                     | Multiplication factor.                                                                                                                                                                  |

|                       |                                                                                                                                                                                         |

6

| $m_{Si}$        | Electron effective mass in the silicon.                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------|

| $m_{SiO_2}$     | Electron effective mass in the silicon dioxide.                                                            |

| μ               | Mobility.                                                                                                  |

| μο              | Low field mobility.                                                                                        |

| µ1/J            | Flicker noise mobility $(\equiv \frac{\mu^3}{\mu_i^2})$ .                                                  |

| $\mu_{after}$   | Mobility after irradiation.                                                                                |

| <b>#before</b>  | Mobility before irradiation.                                                                               |

| µe-e            | Mobility due to electron-electron scattering.                                                              |

| µe[]            | Effective mobility.                                                                                        |

| $\mu_i$         | Mobility due to impurity scattering.                                                                       |

| $\mu_{il}$      | Mobility due to phonon and impurity scattering.                                                            |

| μ               | Mobility due to lattice scattering.                                                                        |

| μ,              | Mobility due to surface scattering.                                                                        |

| µ <sub>SR</sub> | Surface roughness mobility.                                                                                |

| μvs             | Velocity saturation mobility.                                                                              |

| $\mu_n(x,y)$    | Electron mobility in the channel.                                                                          |

| $\mu_{n,p}$     | Mobility; the index $n$ denotes the electrons in NMOSFET and $p$ - holes                                   |

|                 | in PMOSFET.                                                                                                |

| n               | Oxide thickness exponent in the relationship between radiation-induced                                     |

|                 | threshold voltage shift and the oxide thickness.                                                           |

| n               | Inverse subthreshold slope $(\equiv 1 + \frac{C_D(\frac{3}{2}\phi_B) + C_u(\frac{3}{2}\phi_B)}{C_{as}})$ . |

| N               | Total number of free charge carriers.                                                                      |

| No              | Initial value of $N_{e-h}$ (t = 0).                                                                        |

| N <sub>A</sub>  | Acceptor doping concentration in the $p$ -type substrate.                                                  |

| n <sub>bt</sub> | Density of border states per unit volume per eV.                                                           |

| N <sub>M</sub>  | Number of border traps.                                                                                    |

| n,              | Surface density of free carriers.                                                                          |

| Ne-h            | Number of e-h pairs which avoid recombination.                                                             |

| NGATE           | Doping of polysilicon gate electrode.                                                                      |

| n,              | Intrinsic carrier concentration for silicon.                                                               |

| N,              | Sum of all charges in the oxide at zero band-bending ( $\psi_s = 0$ ).                                     |

| Nit             | Number of interface states. $(\psi_s = 0)$ .                                                               |

| Not             | Number of holes trapped in the oxide.                                                                      |

| n,              | Electron concentration at the surface of p-type semiconductor.                                             |

| Ň,              | Number of carriers in the interface states.                                                                |

| N <sub>40</sub> | $N_s$ in the equilibrium state.                                                                            |

| it.             | Surface density of carriers captured in the border traps.                                                  |

| Ň,              | Number of carriers captured in the border traps.                                                           |

| N <sub>t0</sub> | $N_t$ in the equilibrium state.                                                                            |

| NT              | Density of hole traps.                                                                                     |

| u(x,y)          | Density of free electrons in the channel.                                                                  |

| /~/9/           | Radiation frequency.                                                                                       |

| ر               | Angular frequency ( $\equiv 2\pi f$ ).                                                                     |

|                 | $(\equiv \frac{2\pi}{T}, n = 0, \pm 1, \pm 2,).$                                                           |

|                 | $T_T$ , $T_T$ , $T_T$ , $T_T$ , $T_T$ , $T_T$ .<br>Differential operator with respect to the time $(-4)$   |

| )<br>).         | Differential operator with respect to the time $(\equiv \frac{d}{dt})$ .                                   |

| <b>),</b><br>b  | Hole concentration at the surface of <i>p</i> -type semiconductor.                                         |

| *               | Potential at the interface measured with respect to the midgap level.                                      |

.

.

| ψ,                          | Surface potential.                                                            |

|-----------------------------|-------------------------------------------------------------------------------|

| $\psi_{s,inv}$              | Inversion surface potential ( $\equiv 2\phi_B$ ).                             |

| q                           | Electron charge.                                                              |

| $Q(E, \mathcal{E}_{ox}, D)$ | Radiation-induced charge density in the oxide.                                |

| Que                         | Border-trapped charge.                                                        |

| Ŷ,                          | Fixed oxide charge.                                                           |

| $\tilde{Q}_D$               | Charge in the depletion region.                                               |

| Qĩ                          | Charge in the inversion layer.                                                |

| $Q_{it}$                    | Interface-trapped charge.                                                     |

|                             |                                                                               |

| QitFB                       | Interface-trapped charge for flat band condition ( $\psi_s = 0$ ).            |

| Q <sub>m</sub>              | Mobile ionic charge.                                                          |

| Qot                         | Oxide-trapped charge.                                                         |

| Qs                          | Total charge in semiconductor $(\equiv Q_I + Q_D)$ .                          |

| R                           | Resistance $(\equiv G^{-1})$ .                                                |

| R                           | Resistance in the drain circuit $(\equiv \frac{R_D}{1+R_Dg_1})$ .             |

| R                           | Reimbold's factor.                                                            |

| R <sub>D</sub>              | Load resistance.                                                              |

| R <sub>D</sub>              | Drain region extrinsic resistance.                                            |

| R <sub>G</sub>              | Gate bias resistance.                                                         |

| Rj                          | Feedback resistance.                                                          |

| $r(N_t)$                    | Function describing the recombination of carriers.                            |

| R <sub>p</sub>              | Projected range.                                                              |

| R <sub>s</sub>              | Source region extrinsic resistance.                                           |

| 5                           | Subthreshold swing.                                                           |

| 3                           | Time delay.                                                                   |

| $S_{after}(I_{DS})$         | Subthreshold swing after irradiation in the function of the drain current.    |

| $S_{before}(I_{DS})$        | Subthreshold swing before irradiation in the function of the drain cur-       |

| <b>D</b> (() <b>D</b> ()    | rent.                                                                         |

| $S_G$                       | Spectral density of the conductance fluctuations.                             |

| $S_{g}(f)$                  | Spectral density of the generation function.                                  |

| S <sub>IDS</sub>            | Spectral noise power density of the drain current.                            |

| Sids<br>S <sub>N1</sub>     | Power spectral density of the fluctuations of the number of trapped           |

| UN <sub>I</sub>             |                                                                               |

| 8(0)                        | carriers.                                                                     |

| $S_{r}(f)$                  | Spectral density of the recombination function.                               |

| Sth                         | Component independent of frequency representing the thermal noise of          |

| c                           | the system.                                                                   |

| SVDS                        | Spectral noise power density of the drain voltage.                            |

| $S_{\nu_{eq}}(f)$           | Equivalent noise power spectral density in the gate circuit.                  |

| $S_x(f)$                    | Spectral density of the random process $X(t)$ .                               |

| σ                           | Capture cross section.                                                        |

| σ                           | Cross section for the photoelectric effect.                                   |

| <u>t</u>                    | Time.                                                                         |

| Т                           | Period.                                                                       |

| T                           | Temperature.                                                                  |

| ta                          | Body thickness.                                                               |

| t <sub>e</sub>              | Parameter describing inversion layer thickness ( $\equiv \frac{\delta}{4}$ ). |

| tch                         | Effective channel thickness $(\equiv \frac{V_1}{L})$ .                        |

| tar                         | Oxide thickness.                                                              |

| 8                  |                                                                                                                                                              |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| τ                  | Time constant.                                                                                                                                               |

| $\tau_0$           | The shortest time constant.                                                                                                                                  |

| $\tau_1$           | The longest time constant belonging to traps placed in the highest di-                                                                                       |

|                    | stance $x_1$ from interface.                                                                                                                                 |

| $\theta_{c}$       | Drain field reduction parameter.                                                                                                                             |

| θ,                 | Gate field reduction parameter (= $\frac{s_{sio_2}}{1}$ ).                                                                                                   |

| ข้                 | Gate field reduction parameter ( $\equiv \frac{\epsilon_{SiO_2}}{2\epsilon_0 \epsilon_{ar} E_{crit}}$ ).<br>Current exponent in the formula for $1/f$ noise. |

| u                  | Parameter in the complete approximate strong inversion model.                                                                                                |

| υ                  | Parameter in the function describing the mobility profile in the inversion                                                                                   |

|                    | layer ( $\equiv 2\lambda_{eff}$ ).                                                                                                                           |

| $V_{DS}$           | Drain-source voltage.                                                                                                                                        |

| V <sub>DSant</sub> | Saturation drain voltage.                                                                                                                                    |

| V <sub>DSent</sub> | Intrinsic drain saturation voltage.                                                                                                                          |

| V <sub>FB</sub>    | Flat-band voltage.                                                                                                                                           |

| VGB                | Gate-bulk voltage.                                                                                                                                           |

| V <sub>GS</sub>    | Gate-source voltage.                                                                                                                                         |

| $V_{GS}^*$         | Gate voltage at $\psi_s = \frac{3}{2}\phi_B$ .                                                                                                               |

| Vit                | Interface charge component of the threshold voltage.                                                                                                         |

| V <sub>k</sub>     | Kink voltage.                                                                                                                                                |

| V <sub>L</sub>     | $(\equiv F_s L_{eff}).$                                                                                                                                      |

| $V_{\lambda}$      | $(\equiv \mathcal{E}_{hs}\lambda).$                                                                                                                          |

| Vmg                | Midgap voltage.                                                                                                                                              |

| U <sub>n</sub>     | Instantaneous value of the voltage input noise of amplifier.                                                                                                 |

| vo                 | Instantaneous value of the output voltage of preamplifier.                                                                                                   |

| Vot                | Oxide charge component of the threshold voltage.                                                                                                             |

| VSB                | Source-bulk voltage.                                                                                                                                         |

| Vi                 | Thermal voltage $(\equiv \frac{kT}{s})$ .                                                                                                                    |

| Vth                | Threshold voltage.                                                                                                                                           |

| $V_{th\mu}$        | Mobility degradation component of threshold voltage.                                                                                                         |

| V <sub>w</sub>     | n-well voltage.                                                                                                                                              |

| $\overline{V(y)}$  | Channel potential at the point at the distance y from source.                                                                                                |

| Ŵ                  | Nominal gate width.                                                                                                                                          |

| Weff               | Effective gate width.                                                                                                                                        |

| x                  | Coordinate perpendicular to the surface of the interface between $SiO_2$                                                                                     |

|                    | and Si.                                                                                                                                                      |

| $\boldsymbol{x}_1$ | Maximal tunneling distance into the oxide.                                                                                                                   |

| I <sub>d,max</sub> | Maximum depletion width.                                                                                                                                     |

| $\mathbf{x}(t)$    | Noise response at the output of system.                                                                                                                      |

| $\dot{X}(t)$       | Random process.                                                                                                                                              |

| ε                  | Emission probability from the border trap to the interface state.                                                                                            |

| y                  | Coordinate along the length of transistor channel from source to drain.                                                                                      |

| Ŷ                  | Fractional yield $(\equiv \frac{N_{e-h}}{N_{a}})$ .                                                                                                          |

| υ                  | Constant. $(-N_0)$                                                                                                                                           |

| z                  | Coordinate along the width of transistor channel.                                                                                                            |

| Z                  | Atomic number.                                                                                                                                               |

| ζ                  | Capture probability at the border trap from the interface state.                                                                                             |

t<sub>or</sub> Oxide thickness.

•

# Chapter 1

## Introduction

The radiation hardness of electronics has recently become a very important issue not only in military and space applications, but also in large experiments of high energy physics which are carried out in order to understand the most fundamental structures of matter. It concerns the semiconductor detectors used in these experiments and the VLSI technologies used to construct readout electronics. ASIC components have proved very useful in building fast analog front-end electronics coupled to big systems of radiation detectors needed in these experiments to observe what happens in elementary particle collisions. The front-end electronics systems (preamplifiers, comparators, analog memories, buffers, pipelines, analog-to-digital converters) must be mounted very close to detectors to avoid many long cables for the transmission of analog signals. The silicon VLSI technologies are very beneficial to solving such problems. However, these systems are exposed to radiation to a significant level. Therefore the choice of more radiation tolerant silicon devices to construct such electronic systems is necessary. This study aims at providing arguments to make this choice possible.

The work presented here is the result of study carried out by the author during his work in the ZEUS detector group at DESY in Hamburg. During that time several other reports dedicated to the same goal and prepared by the author's co-workers were published at DESY [5, 6, 7, 8]. The results were also presented at the conferences [9, 10].

The main part of the ZEUS experiment is high resolution uranium sampling calorimeter surrounding the pipe of the HERA collider near the e-p interaction point. This calorimeter consists of 10 000 depleted uranium plates separated by 240 000 scintillator tiles. The uranium plates and scintillator tiles form the so-called "sandwich" structure, where alternate layers perform a stepwise process of shower development and signal generation. The light leaving the scintillator tiles is collected by sheets of a plastic wave length shifter which transports the light. Then, this optical signal is directed to the light sensitive cathodes of phototubes. In this way, the energy deposited in the calorimeter results in a current signal of the photomultipliers anodes. This analog electrical signal is directed to the analog front-end card which consists mainly of two ASIC chips: a pipeline and a buffer-multiplexer. The signal at the analog card is triggered to eliminate signals which are non-interesting for physics. After leaving the front-end electronics the information from calorimeter has to be digitized and filtered. The total construction weights c. a. 700 tons and has 12 000 readout channels.

The pipelining and buffering is realized by means of switched-capacitor technique. The pipeline chip stores the sampled data of the preceding  $5\mu$ s (for a sampling rate 10.4 *MHz*; a memory depth of 58 cells has been chosen). The second stage of the pipeline system consists of a buffer storage, which is similar to the main pipeline channels. The third stage is an analog multiplexer, which is capable of switching 12 buffered and one unbuffered (stand-by) channels to one output and a further 12 unbuffered channels to a second output [1, 2]. These two stages are integrated on one chip.

In order to fabricate these two chips the MOS technology has been chosen due to the following advantages. The fabrication process is simple, well known and cheap in comparison with bipolar and BiMOS technologies. A very high integration of devices and very low power consumption can be achieved. The switched-capacitor technique needs a lot of capacitors and switches and MOS technology is very good one for integrating capacitors and switches. MOS transistors make one of the best switch available in integrated-circuit form. They require little area, dissipate very little power, and provide reasonable values of  $R_{ON}$  (range from several  $k\Omega$  to  $100 \Omega$ ) and  $R_{OFF}$  ( $\approx 10^{12} \Omega$ ) [3]. Although MOS transistors exhibit very large 1/f low frequency noise, in the range of high frequency (above mentioned 10.4 MHz) a noise problem does not appear. The combination of analog and digital circuits on one chip does not create any additional problems.

One of the most important problems which should be solved for such applications of MOS technology is that of radiation hardness. The dose rate due to synchrotron radiation at the position of the calorimeter or its electronics should everywhere be smaller then 1 krad/year. Only in some places, very close to the beam pipe, the dose rate could be  $\approx 10 \, krad/year$ . The dose rate due to high energy neutrons is estimated on the level of 60 rad/year [4]. The neutron radiation is dangerous only for junction devices with respect to creation of atomic displacements in the crystal lattices caused by the collisions of fast neutrons with silicon atoms. For MOS transistors this kind of radiation effects is not very important because electrical current flows only in a very thin surface layer of silicon under gate oxide. The second kind of radiation damages are ionization effects which are caused mainly by photonic radiation like x-ray,  $\gamma$ or synchrotron radiation. Radiation passing the insulator generates charges which influence the electrical characteristics of the transistor.

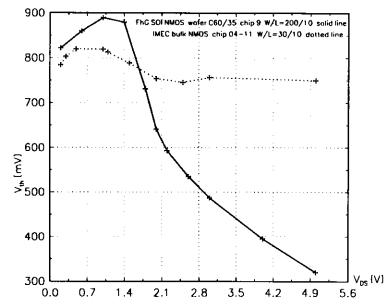

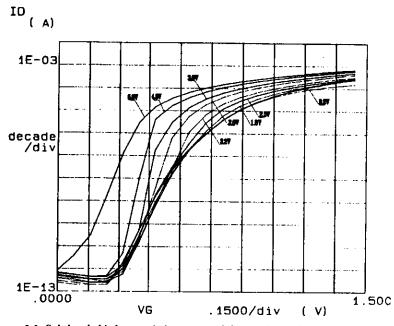

The necessity of undertaking the study presented here appeared while testing several technologies which application in the fabrication of the two analog chips described above had been planned. The main task of this study is to examine ionizing effects in MOS transistors in their physical, technological and measuring aspects. The results of the measurements carried out are related to several MOSFET parameters: threshold voltage  $V_{th}$ , transconductance  $g_m$ , subthreshold swing S and spectral noise power density of drain current  $S_{I_{DS}}(f)$ . However, the most visible radiation effect of tested technologies is the distortion of the subthreshold characteristic due to leakage currents. A great deal of attention is focused on the radiation behaviour of the kink

effect in a SOI technology.

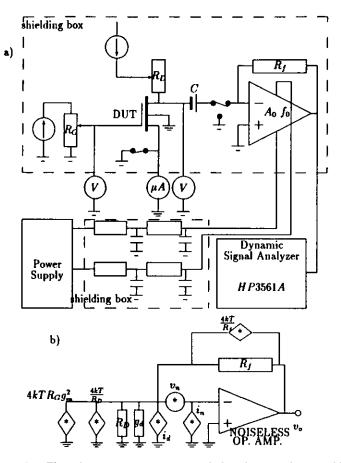

The test procedure used here consists in the subsequent irradiations and measurements of test structures. For irradiation the  $Cs^{137}$  source of activity A = 5Ci and energy of  $\gamma$  quants  $E_{\gamma} = 661 keV$  was used. A homemade system was constructed for measurements [5]. It was controlled by VME-137 computer running under program written in C language. One part of results was obtained by means of using a semiconductor parameter analyzer a HP4145B. The noise measurements were taken by a dynamic signal analyzer a HP3561A. For data acquisition a standard GPIB interface between instruments and a computer was adopted.

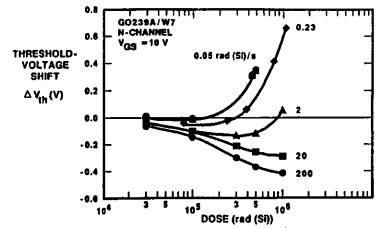

The dose rate used while irradiating test structures was  $\approx 2.9 \ krad/h$  and it allowed the achievement of a total absorbed dose at the level of 200 krad during several days of irradiation. Such a dose highly exceeded the one predicted for the ZEUS detector. On the other hand, the total doses that were used were very low in comparison with modern requirements for future high energy physics experiments at the LHC or SSC: 10 Mrad. Such requirements for a total dose are far larger than those for space applications (100 krad) and defence applications (0.1  $\div$  1 Mrad). The dose rate used in another similar study at CERN [12] reached  $\approx$  290 krad/h.

In comparison with the total dose values mentioned above, the predictions for the ZEUS detector are relatively small. Therefore, the electronic technologies dedicated for ZEUS are standard, not hardened processes developed by IMEC, ELMOS and FhG IMS. The results obtained from irradiations and measurements of these technologies are presented in this study.

The amount of the data gathered was so large that only a small part of it can be presented here. Particular attention was paid to the SOI technology because it is a newer version of a modern MOS technology which is still being developed. All graphs demonstrated here are the result of original measurements obtained by the author unless stated otherwise.

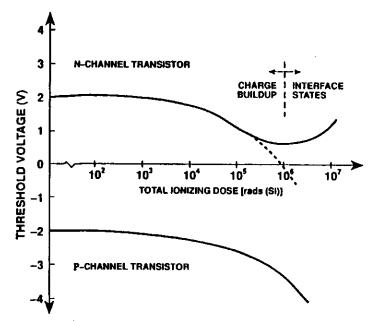

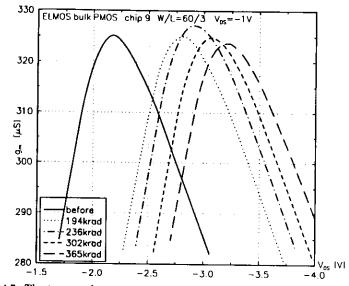

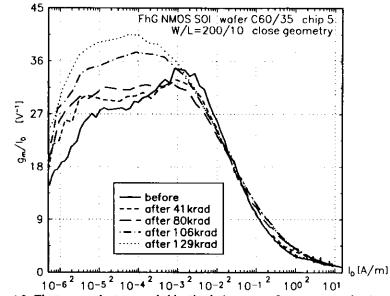

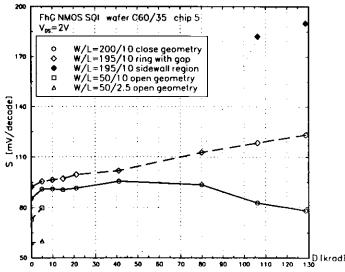

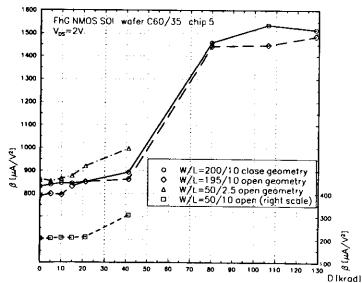

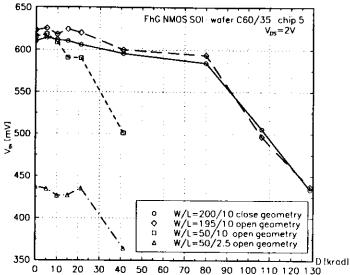

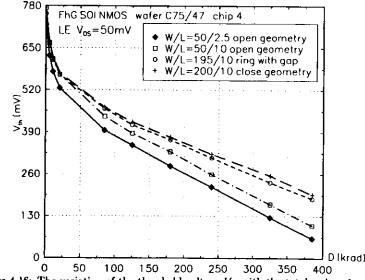

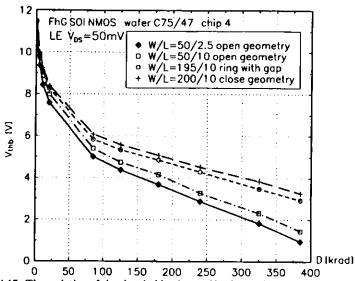

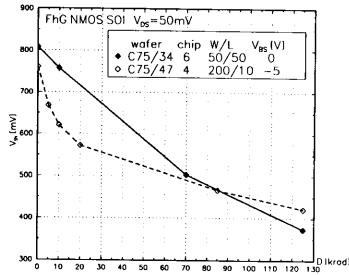

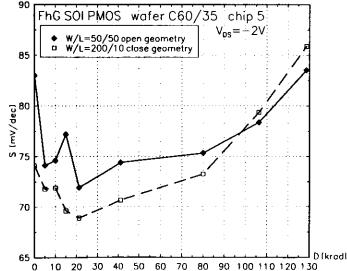

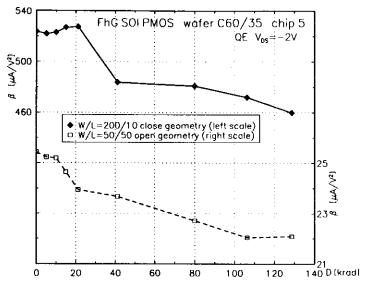

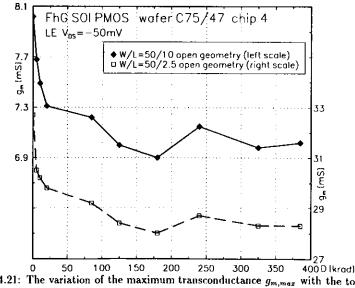

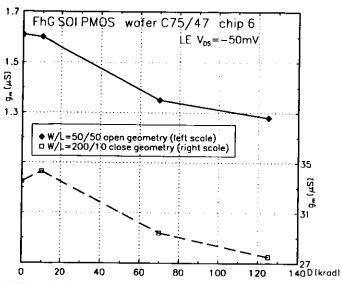

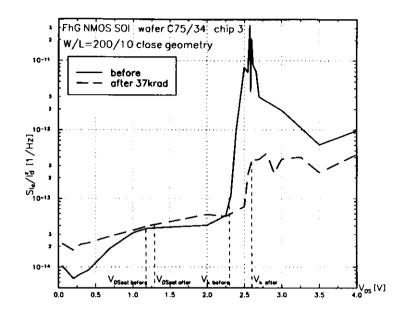

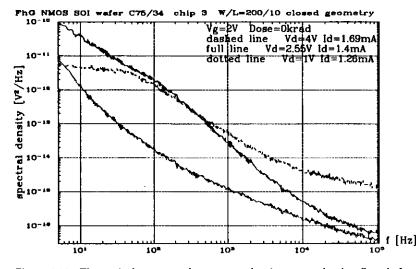

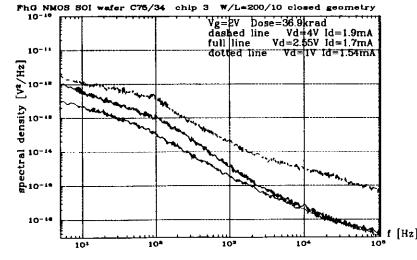

Chapter 2. describes shortly the structure and parameters of a MOS transistor. Commonly used models of a MOS transistor operating in above- and sub-threshold regions are presented in appendices. Typical process flows of MOS bulk and SOI technology are discussed in chapter 3. A great deal of attention is paid to technological details because this subject has not been consider in previous publications at DESY. Each technological step is illustrated by process parameters used at the Fraunhofer Institute in Duisburg. These parameters are: implantation energy, dose of implanted dopants, oxidation temperature, annealing temperature, oxidation time, annealing time, thickness of layers, composition of oxidation atmosphere, velocity of gas flow. concentrations of dopants, resistivity of layers and others. This review of technology gives opportunity for understanding the influence of technological parameters on radiation sensitivity. Therefore this chapter also contains a review of technological efforts undertaken to improve the radiation hardness which are presented in many articles. The next chapter deals with the physical mechanisms of creation of radiation damages in silicon dioxide. It contains also the presentation of the results obtained for electrical MOSFET parameters. The most important MOSFET parameter which was studied in the function of  $\gamma$  dose is the threshold voltage. The radiation-induced change of transconductance as a parameter  $\beta$  of model equation and as a maximal value  $g_{m,max}$  in the linear range of transistor operation was also observed. The methods of separation of two components of threshold voltage caused by oxide charge and interface charge are presented and illustrated by original measurement data. The results of the SOI transistors concern various transistor structures and bias conditions and the back gate parasitic transistor. The changes of the kink effect point and the parameter f describing the kink effect were observed for n- and p-channel transistors. The results concerning noise properties of irradiated MOSFETs are presented in chapter 5. together with a review of flicker noise theory. The changes of noise power spectrum caused by irradiation were observed. Three parameters of noise spectrum: the noise level, the frequency exponent and the thermal noise component were fitted.

### Chapter 2

# Ideal and nonideal MOS structure

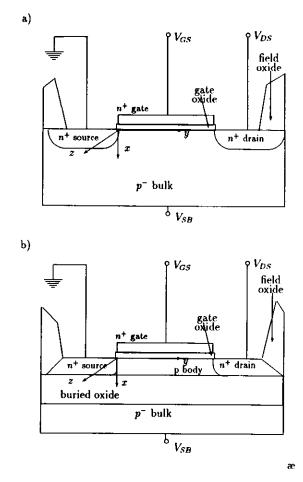

A MOS structure (Fig. 2.1) consists of three subsequent stacked layers:

- a gate electrode made of a conductor like Al or p- or n-type poly-Si;

- an insulator separating the upper conducting layer from the semiconductor below made of silicon dioxide  $SiO_2$ , silicon nitride  $SiN_3$  or a nitride/oxide doublelayer;

- a semiconductor substrate made of p- or n-type crystalline silicon Si.

This means that the two most important materials are Si and  $SiO_2$ . The table below (Tab. 2.1) summarizes the electrical and physical parameters of these two materials.

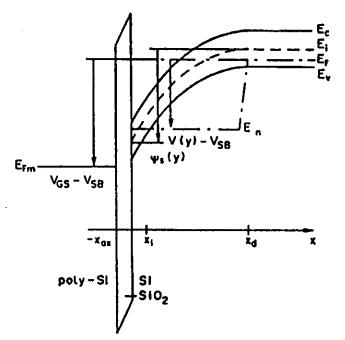

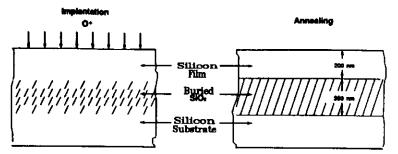

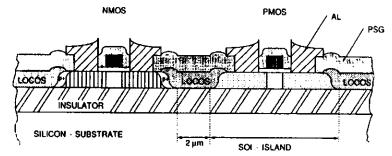

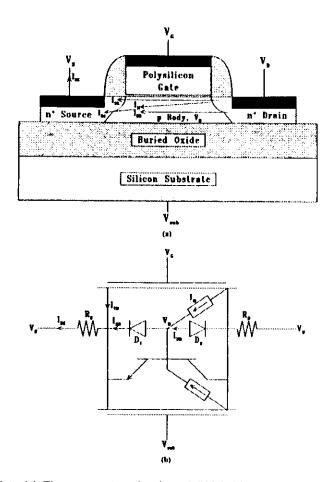

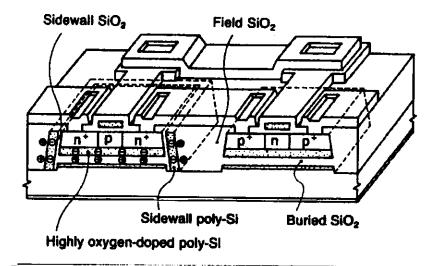

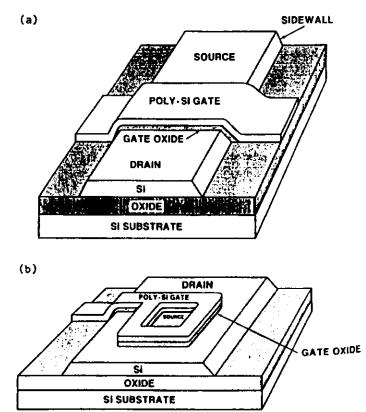

Idealized MOS n-channel transistor structures for bulk and SOI version are shown on Fig. 2.1. The band diagram for such structures near the source area where V(y) = 0is shown on Fig. 2.2. The radiation effects are related to nonidealities present in the oxide layers. We can distinguish three types of oxide layers:

- **gate-oxide** a thin  $(40 \div 15 \text{ nm}) \text{ SiO}_2$  layer between the gate electrode and the transistor channel, covering the area  $W \times L$ , fabricated by the thermal oxidation of the silicon layer;

- field-oxide a thick  $(500 \div 1000 \text{ nm})$  SiO<sub>2</sub> layer covering the whole silicon area not occupied by active devices; fabricated by thermal oxidation (LOCOS) or chemical vapour deposition; the task of such a layer is the lateral separation of adjacent devices;

- **buried-oxide a thick**  $(150 \div 500 \text{ } nm) \text{ } SiO_2$  layer separating a device body from the substrate in a vertical direction, fabricated by oxygen ion implantation into

- the silicon wafer (SIMOX); used only in SOI technologies.

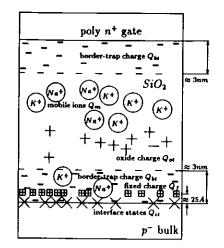

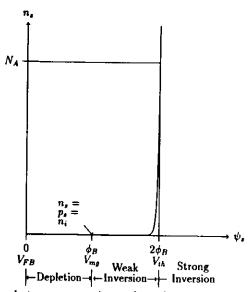

The nonidealities are charges and electronic states which exist in the oxide and at the  $Si - SiO_2$  interface. The standard classification and terminology for them proposed in 1980 by Deal committee [17] and supplemented recently by Fleetwood [18] is presented in Fig. 2.3. In general, these charges can be split in two groups. The charges of the first type  $(Q_{oi}, Q_j)$  cannot interact with free carriers existing in the underlying silicon, but the charges of the second type  $(Q_{ii}, Q_{bi})$  are in an electrical communication with the silicon and can be charged or discharged, depending on the surface potential. Such electron states show acceptor or donor properties. Donor states are positively charged when empty (above Fermi level), and neutral when filled

Figure 2.1: The ideal MOS n-channel transistor structure: a) bulk technology, b) SOI technology.

Table 2.1: Properties of intrinsic silicon Si and silicon dioxide SiO<sub>2</sub>.

All other values without references are given according to [13].

If in the table below only one value is given, it means that this value was measured at a temperature of 300°K.

If a range is given, it indicates that the quantity is temperature and field dependent in the specified range.

| Material                                                                         | Si                                                 | SiO <sub>2</sub>                   |

|----------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------|

| Туре                                                                             | Semiconductor                                      | Insulator                          |

| Crystal structure                                                                | Diamond                                            | Random tetrahedra                  |

|                                                                                  | 8 atoms                                            | 1 Si and 4 O atoms                 |

| A / 1 1                                                                          | per unit cell                                      | per unit cell [14]                 |

| Atomic/molecular weight                                                          | 28.09                                              | 60.08                              |

| Atomic/molecular<br>density (10 <sup>22</sup> cm <sup>-3</sup> )                 | 5.0                                                | 2.3                                |

| Lattice constant (A)                                                             | 5.43                                               | 5.03                               |

| Spacing to the nearest                                                           | 2.35 (Si-Si)                                       | 1.62 (Si-O)                        |

| neighbour (A)                                                                    | 2.00 (01-01)                                       | 2.62 (0-0)                         |

| 0 . (-7                                                                          |                                                    | 3.12 (Si-Si) [14]                  |

| Density $(gcm^{-3})$                                                             | 2.33                                               | 2.27                               |

| Work function $\Phi$ (eV)                                                        | 4.1-5.2                                            | -                                  |

| Electron affinity $\chi$ (eV)                                                    | 4.1                                                | 0.9                                |

| Band gap energy $E_g$ (eV)                                                       | 1.11                                               | 8.5                                |

| Hole-electron pair                                                               |                                                    |                                    |

| generation energy $E_i$ (eV)                                                     | 3.6                                                | 17.0±1                             |

| Effective density of (10 <sup>19</sup> cm <sup>-3</sup> )                        | 2.80                                               | · ·                                |

| - states in conduction band $N_e$<br>- states in valence band $N_e$              | 2.80                                               |                                    |

| Intrinsic carrier                                                                | 1.01                                               |                                    |

| concentration $n_i$ (10 <sup>10</sup> cm <sup>-3</sup> )                         | 1.483                                              | -                                  |

| Diffusion coefficient of $(cm^2s^{-1})$                                          |                                                    |                                    |

| - electrons D <sub>n</sub>                                                       | 35.0                                               |                                    |

| - holes <i>D</i> ,<br>Mobility of                                                | 12.5                                               |                                    |

| - electrons $\mu_{-}$ ( $cm^2V^{-1}s^{-1}$ )                                     | 1350                                               | 20÷40 [15]                         |

| - electrons $\mu_n$ $(cm^2V^{-1}s^{-1})$<br>- holes $\mu_p$ $(cm^2V^{-1}s^{-1})$ | 480                                                | $10^{-4} \div 10^{-11}$ [15]       |

| Dielectric constant $\epsilon$                                                   | 11.7                                               | 3.9                                |

| Dielectric permittivity $\varepsilon \varepsilon_0 (10^{11} F cm^{-1})$          | 0.104                                              | 0.0345                             |

| Breakdown field ( $V/\mu m$ )                                                    | 30                                                 | 600                                |

| Melting point (°C)                                                               | 1415                                               | 1650                               |

| Vapour pressure (torr), at                                                       | 10 <sup>-7</sup> , 1050<br>10 <sup>-5</sup> , 1250 | $10^{-3}, 1450$<br>$10^{-1}, 1750$ |

| temp. (°C)                                                                       |                                                    |                                    |

| Specific heat $C_h(J/g^\circ C)$                                                 | 0.70                                               | 1.0                                |

| Thermal conductivity                                                             |                                                    | 0.014                              |

| $K_{ih} (W/cm^{\circ}C)$                                                         | 1.5                                                | 0.014                              |

| L                                                                                |                                                    | _ <u></u>                          |

|      |       |       |      |      |     | <b>~</b> • | •   |

|------|-------|-------|------|------|-----|------------|-----|

| - 11 | Conti | nuati | on o | l ta | hle | 2.1        | . 1 |

|      |       |       |      |      |     |            |     |

| Material                                                                                          | Si                                                                        | $SiO_2$                     |

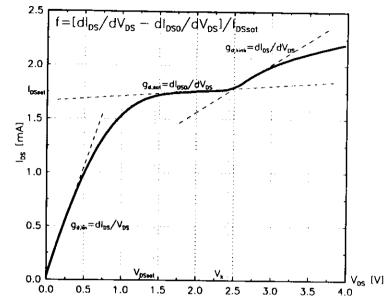

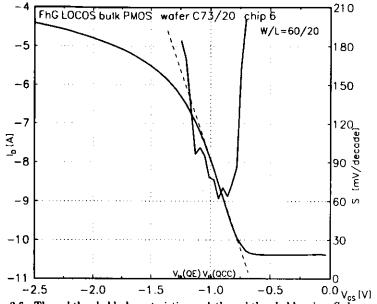

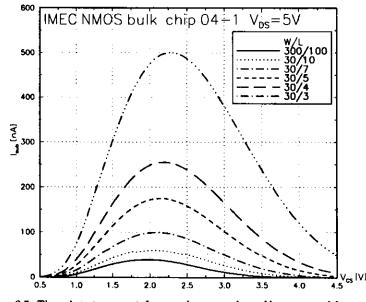

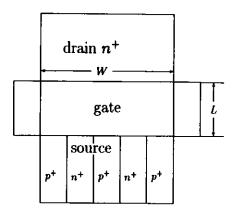

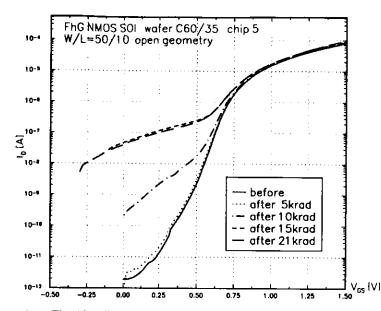

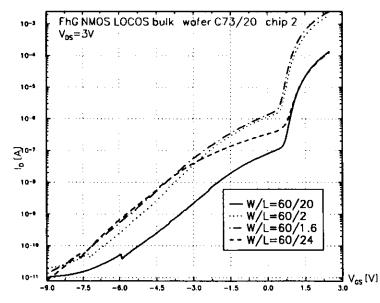

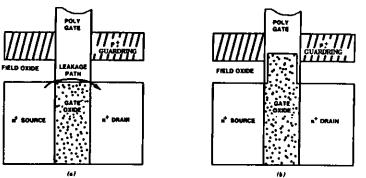

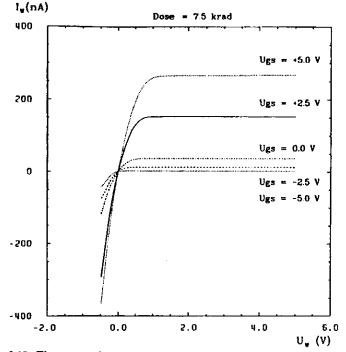

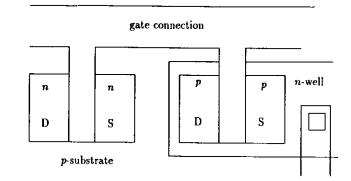

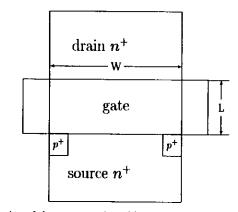

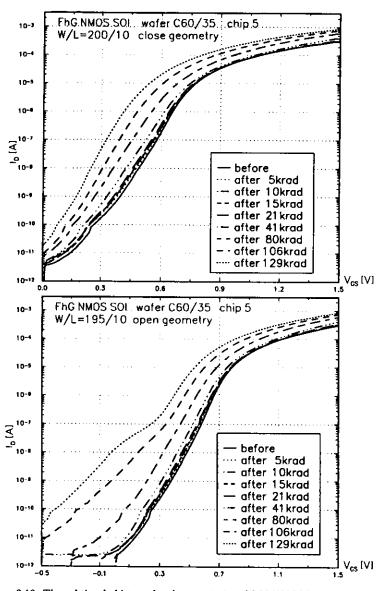

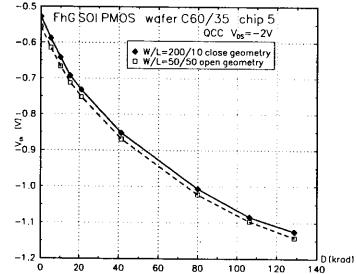

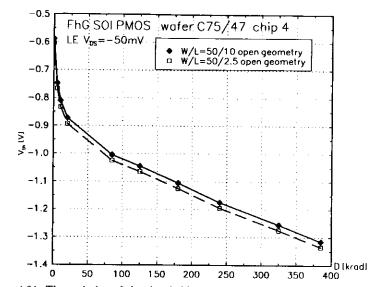

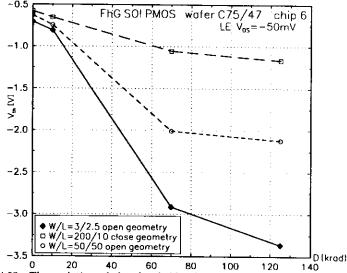

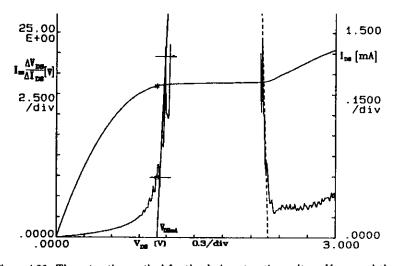

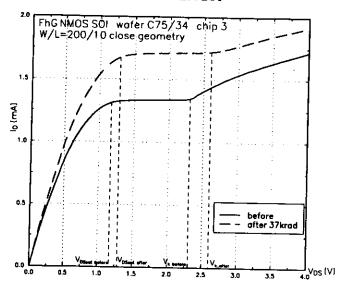

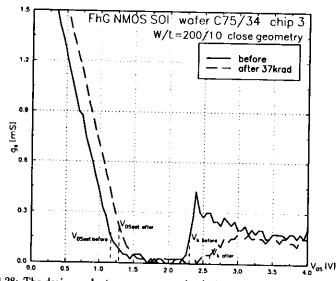

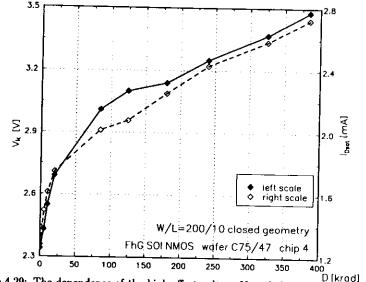

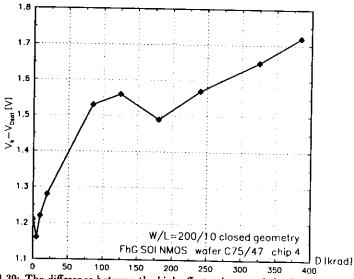

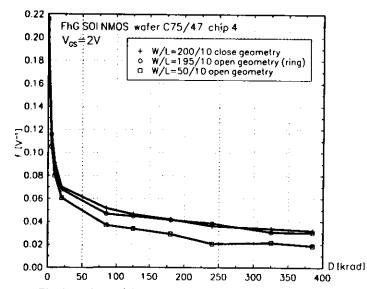

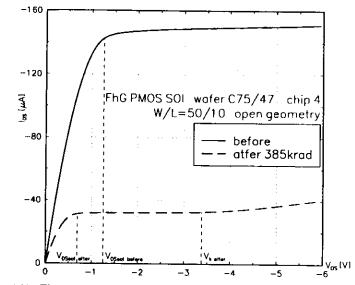

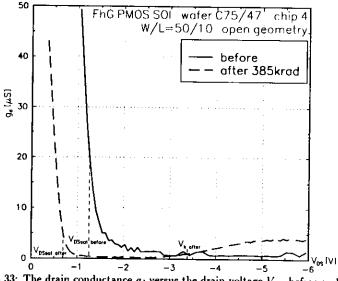

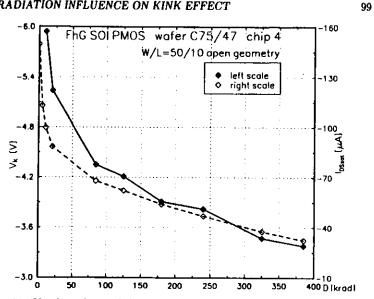

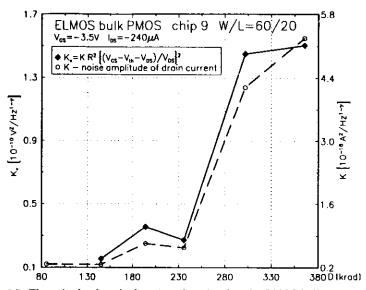

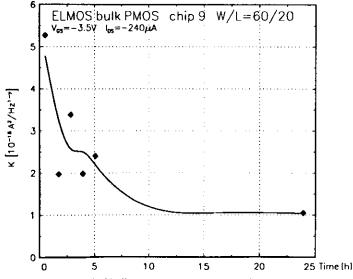

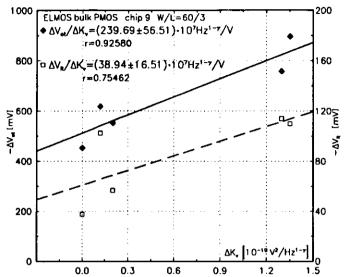

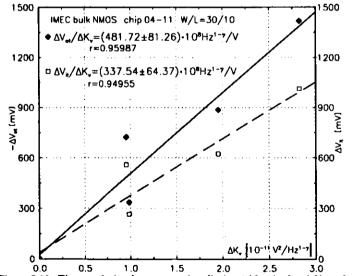

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------|